# **B 1700**

# **CENTRAL SYSTEM**

# Burroughs

FIELD ENGINEERING

# TECHNICAL MANUAL

3

INTRODUCTION AND OPERATION

FUNCTIONAL DETAIL

CIRCUIT DETAIL

**ADJUSTMENTS**

MAINTENANCE PROCEDURES

INSTALLATION PROCEDURES

RELIABILITY IMPROVEMENT NOTICES

OPTIONAL FEATURES

Burroughs

# COPYRIGHT © 1972, 1973 BURROUGHS CORPORATION Detroit, Michigan 48232 AA401141 AA470338

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

# INDEX

# Page No.

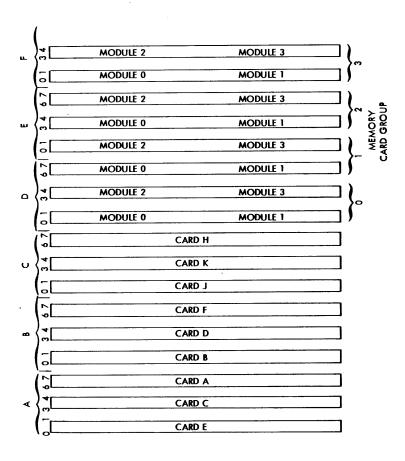

| INTRODUCTION AND OPERATION – SECTION I         | System Interrupt                                 |

|------------------------------------------------|--------------------------------------------------|

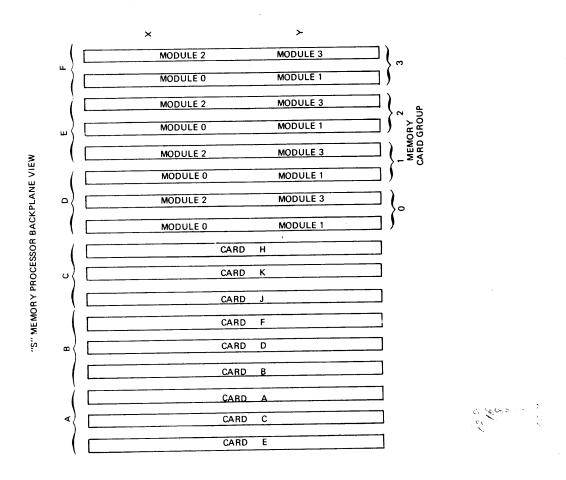

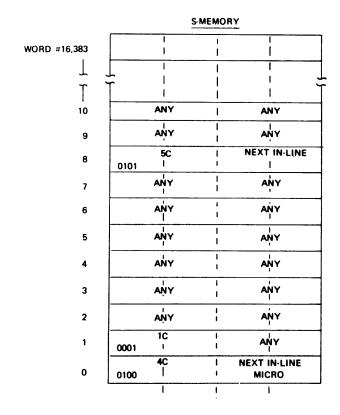

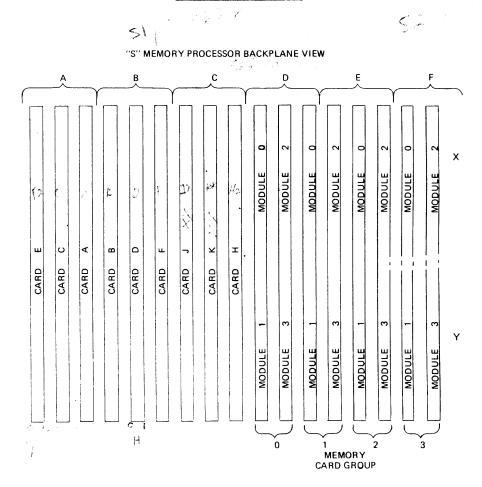

|                                                | S-Memory (System Memory)                         |

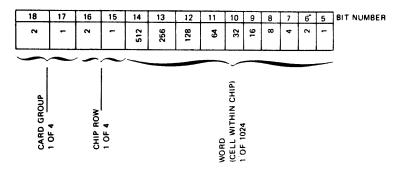

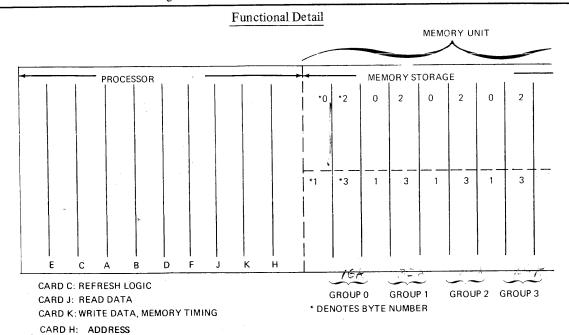

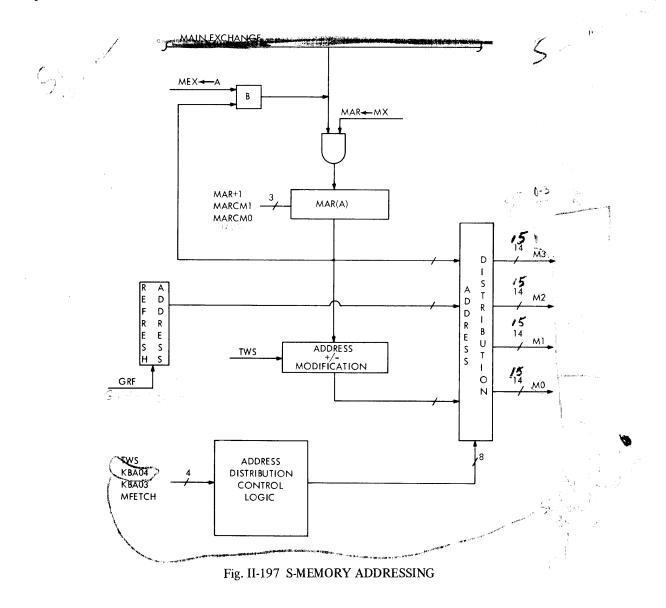

| B1700 Central System                           | Address Distribution Logic 29                    |

| Basic Software Overview                        | Associated Memory Registers                      |

| Interpreter                                    | Memory Address Logic                             |

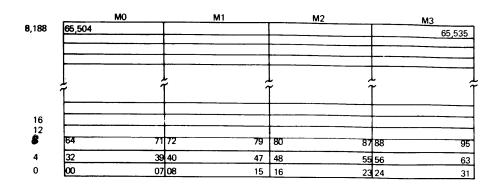

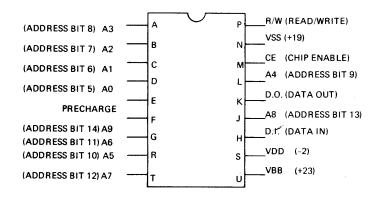

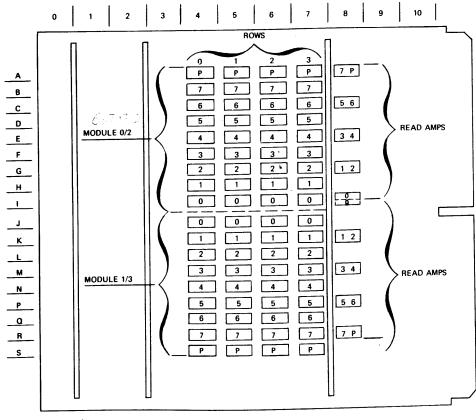

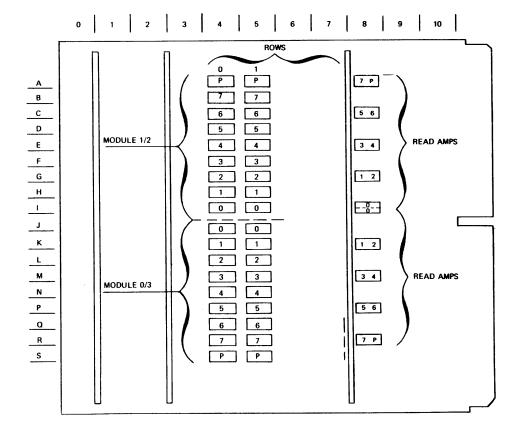

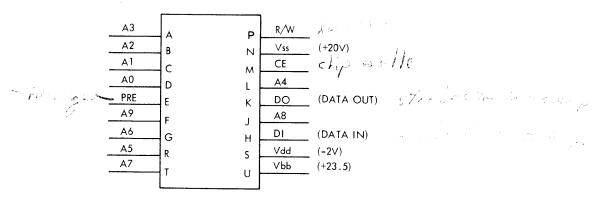

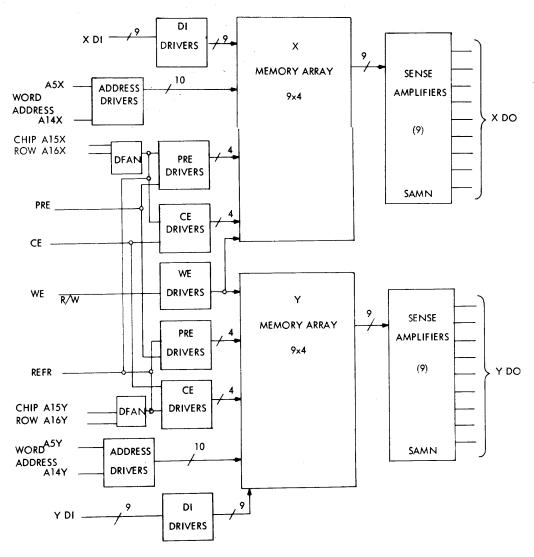

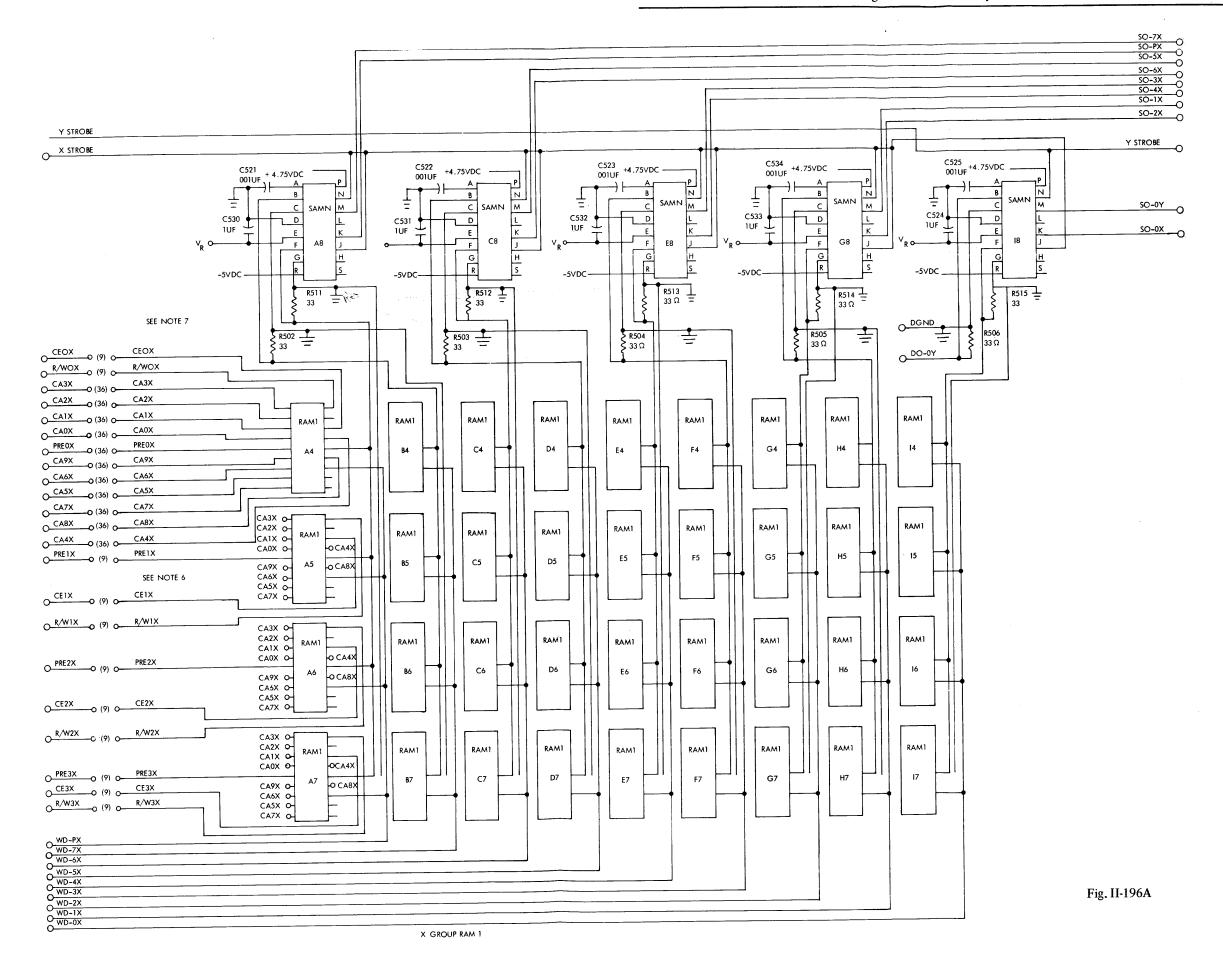

| Program Storage                                | Memory Chips (RAM) 27                            |

| S-Language                                     | Memory Grouping 27                               |

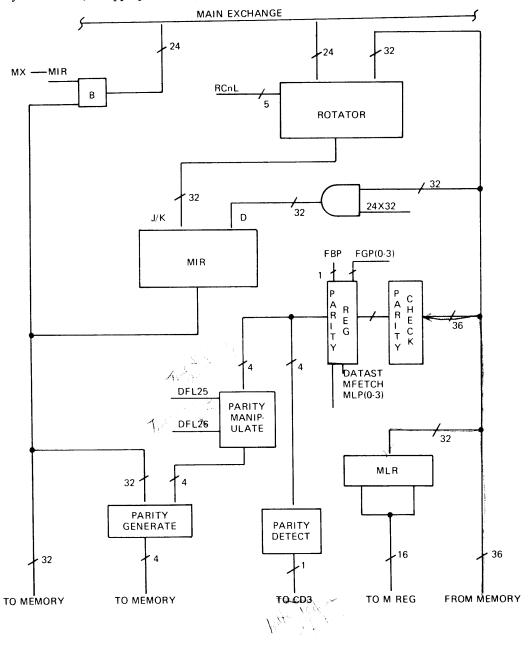

| Glossary of Terms                              | Memory Information Logic and Rotator 30          |

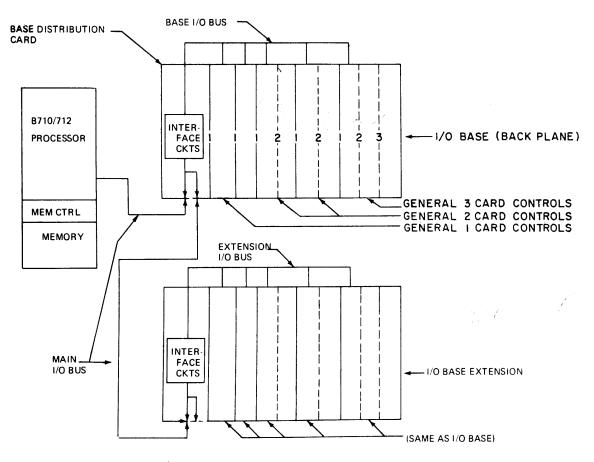

| I/O Subsystem                                  | Memory Information Register (MIR) 30             |

| Introduction 1                                 | Memory Latches (MLR)                             |

| Macro Instruction                              | Memory Size                                      |

| _                                              | Parity                                           |

| Micro Histiaction                              | Refresh                                          |

| Micro Frogramming                              | Rotator                                          |

| Micro Operators                                | Storage Board                                    |

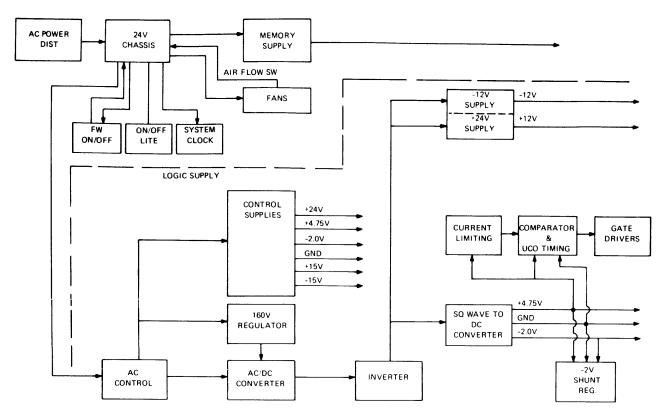

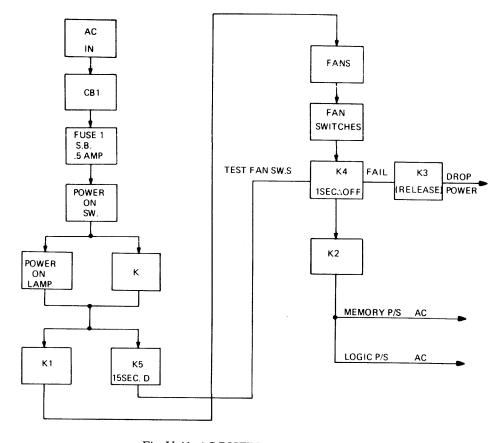

| Power Distribution                             | Storage Doard                                    |

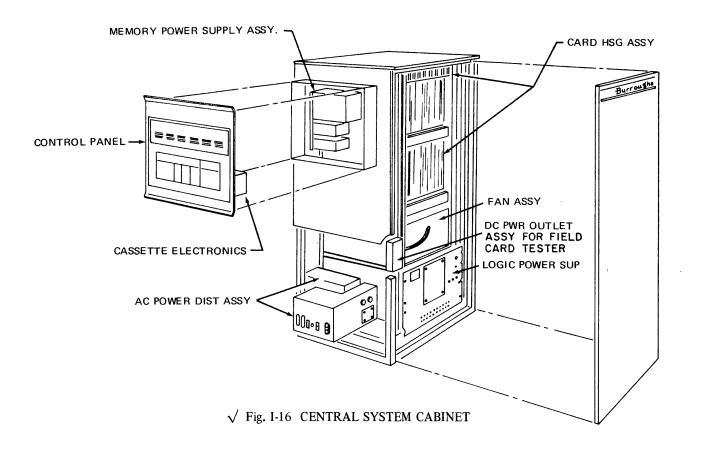

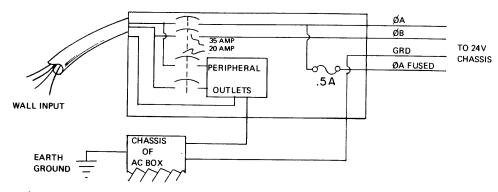

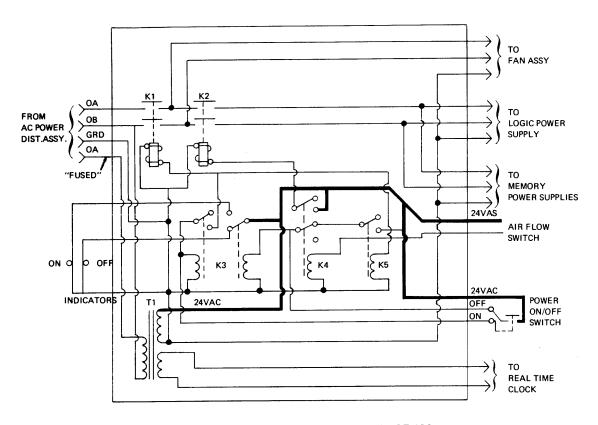

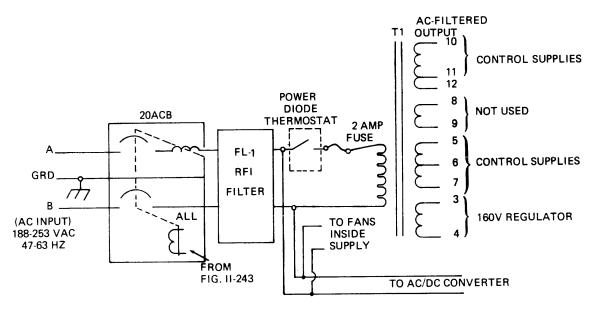

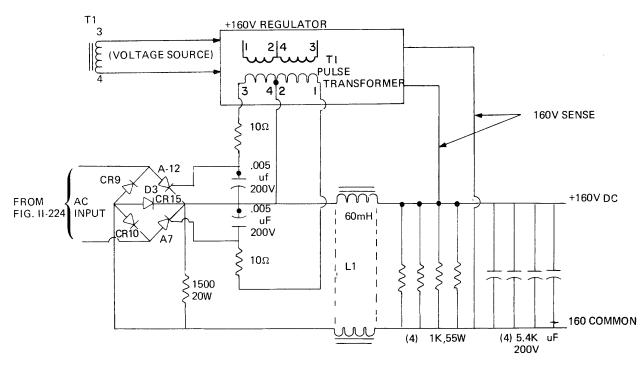

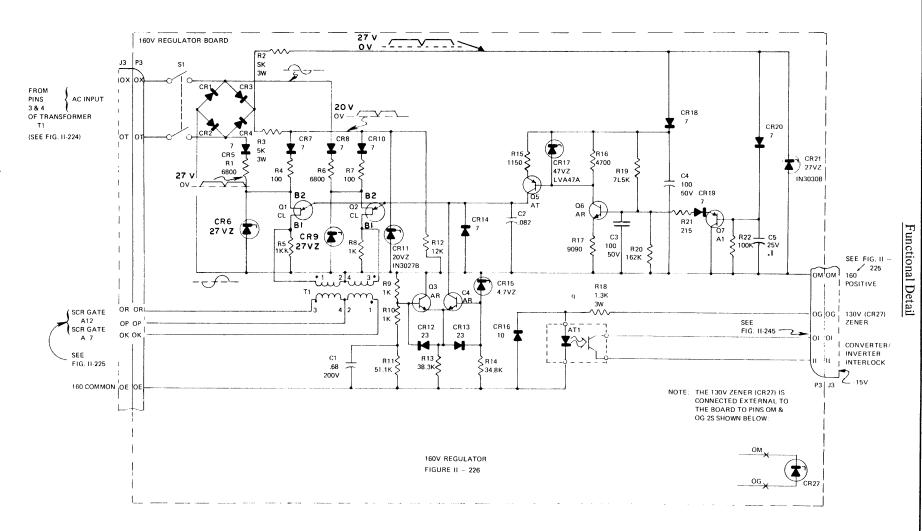

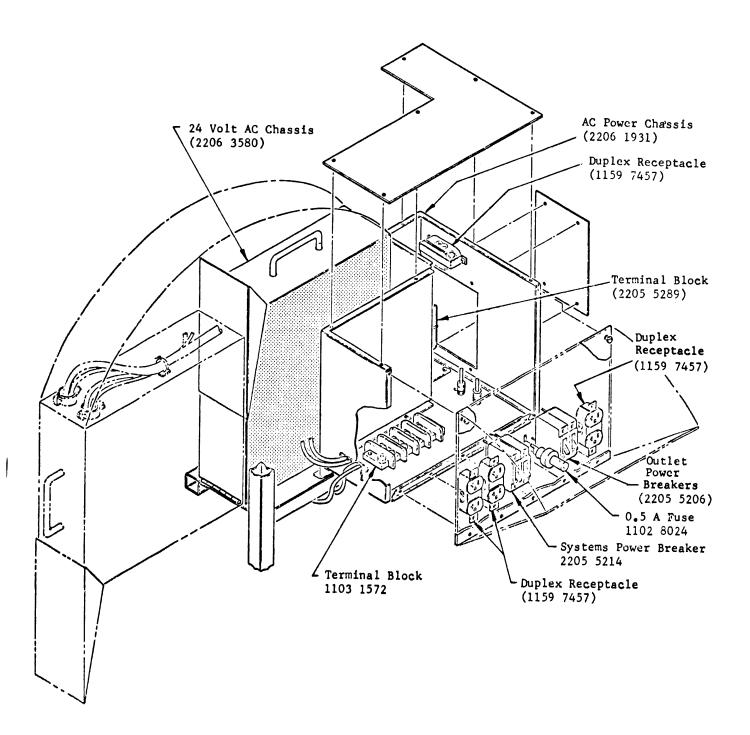

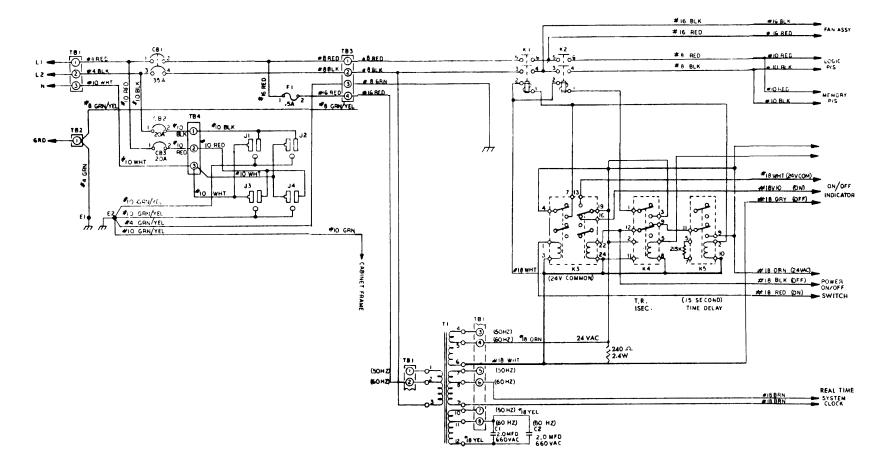

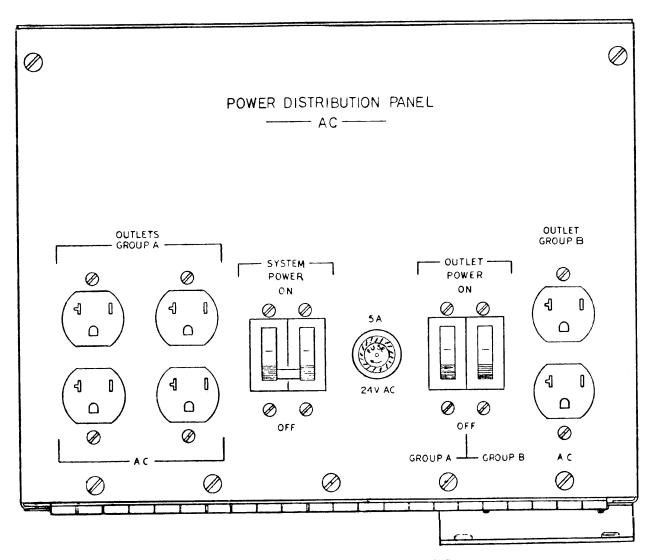

| A.C. Power Distributing Assembly 33            | FUNCTIONAL DETAIL - SECTION II                   |

| Memory Power Supplies                          | TONCTIONAL DETAIL - SECTION II                   |

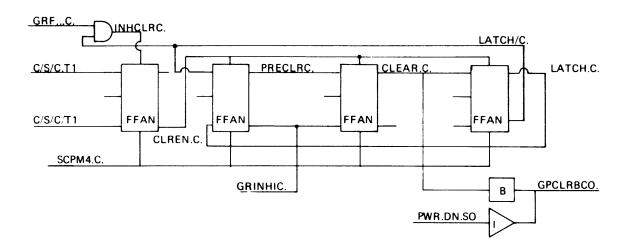

| Power Operation                                | Address Distribution                             |

| Processor 2                                    | Address Distribution Control                     |

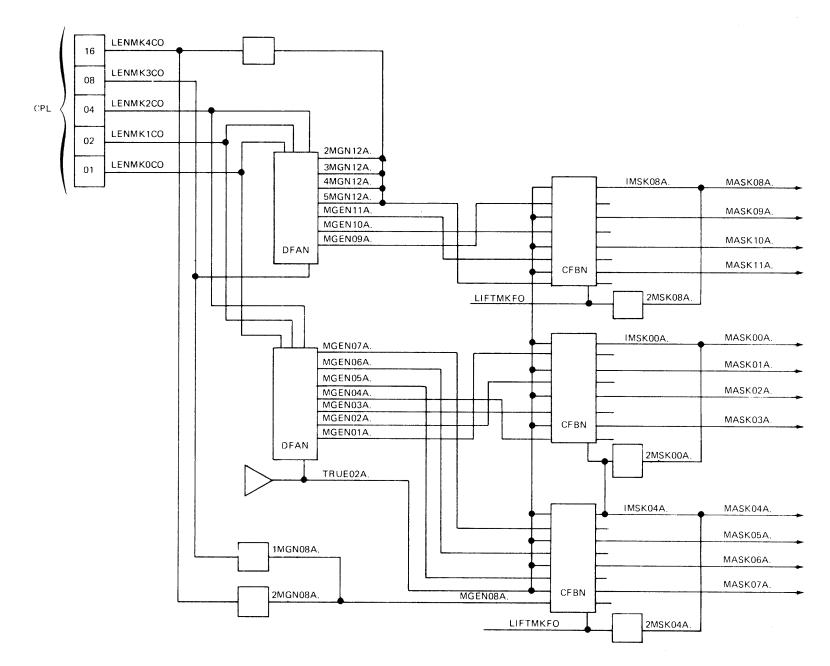

| 24 Bit Arithmetic and Combinatorial Unit       | Address Modification Logic                       |

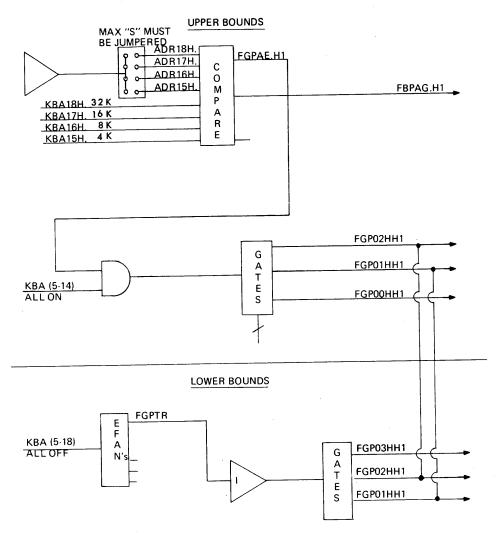

| (24 Bit Function Box) 5                        | Address Out of Bounds Logic                      |

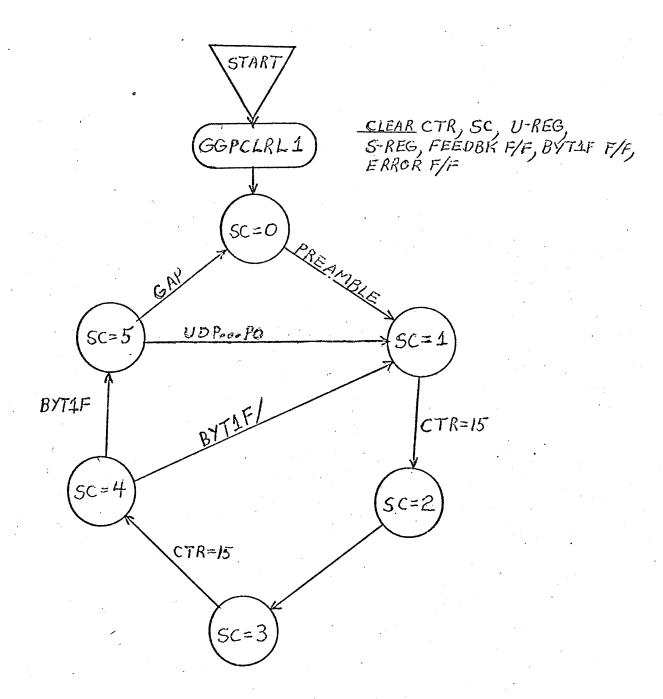

| Cassette Tape 3                                | Basic Machine States                             |

| Console                                        |                                                  |

| Four Bit Arithmetic and Combinatorial Unit     |                                                  |

| (Four Bit Function Box) 6                      |                                                  |

| Local Memory 4                                 |                                                  |

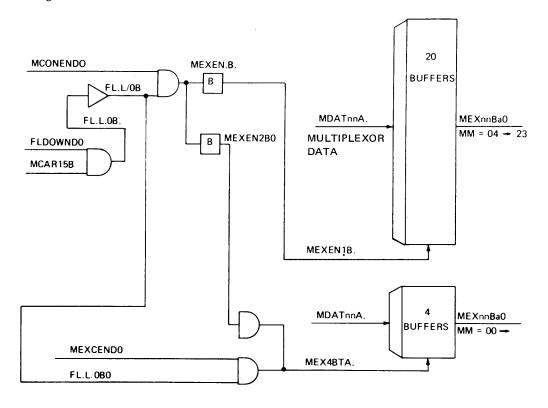

| Main Exchange (MEX) 4                          |                                                  |

| Registers                                      | Interfacer                                       |

| A Stack                                        | Cassette Positioning                             |

| BR and LR Register (Base and Limit Register) 9 | Cassette Rewind Logic                            |

| C Register (Control Register) 10               | Cassette Serial Date Assembly                    |

| CMND Register (Command Register) 11            | Cassette Start Logic                             |

| Data Register                                  | Cassette Stop Logic                              |

| FA Register (Field Address Register) 9         | Execution of Micros 118                          |

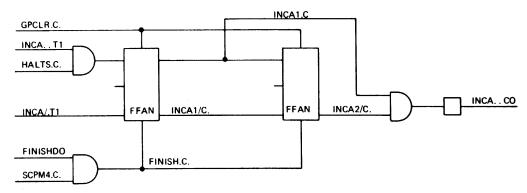

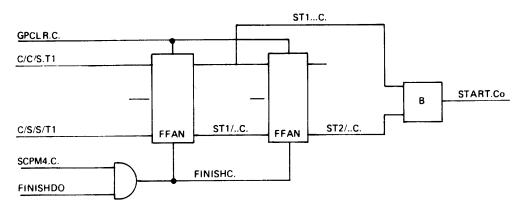

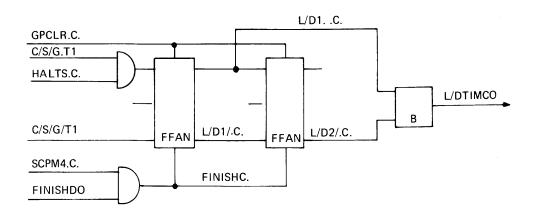

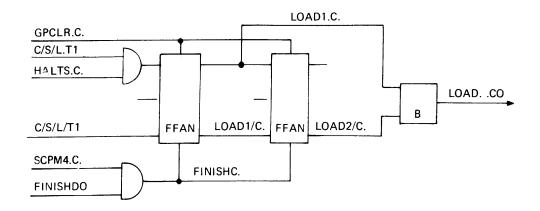

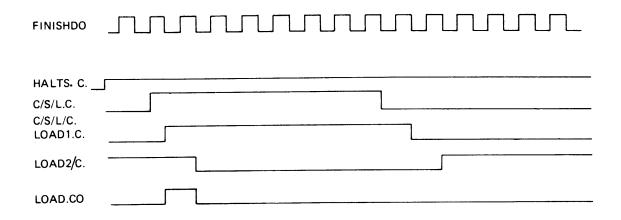

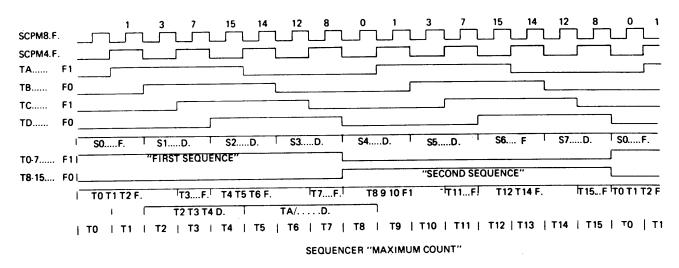

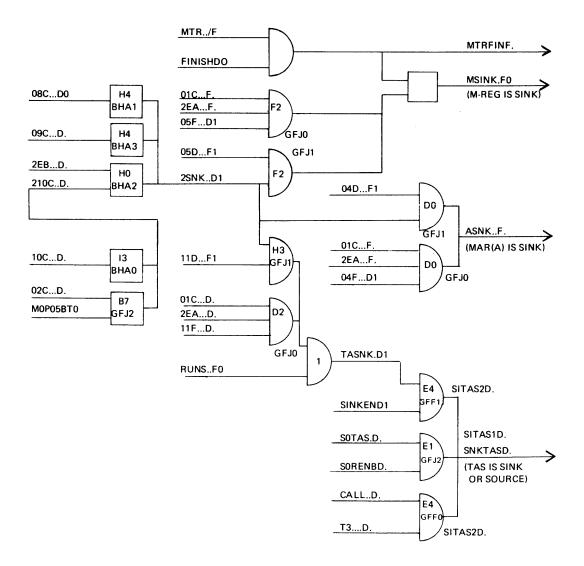

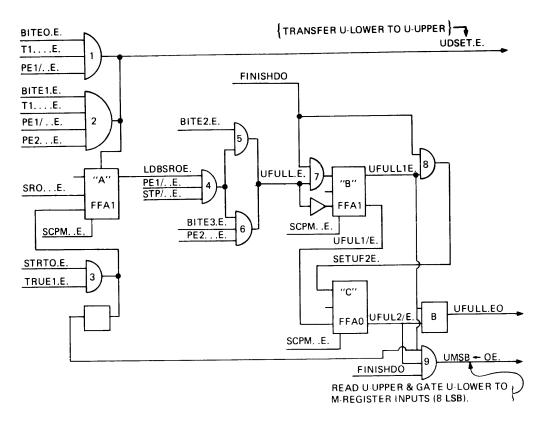

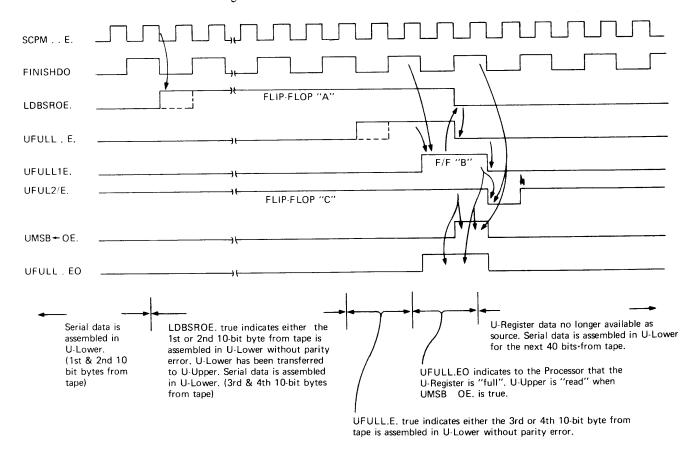

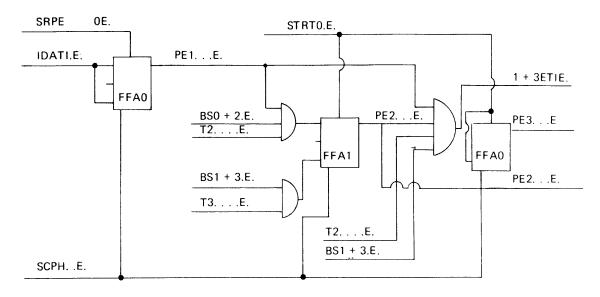

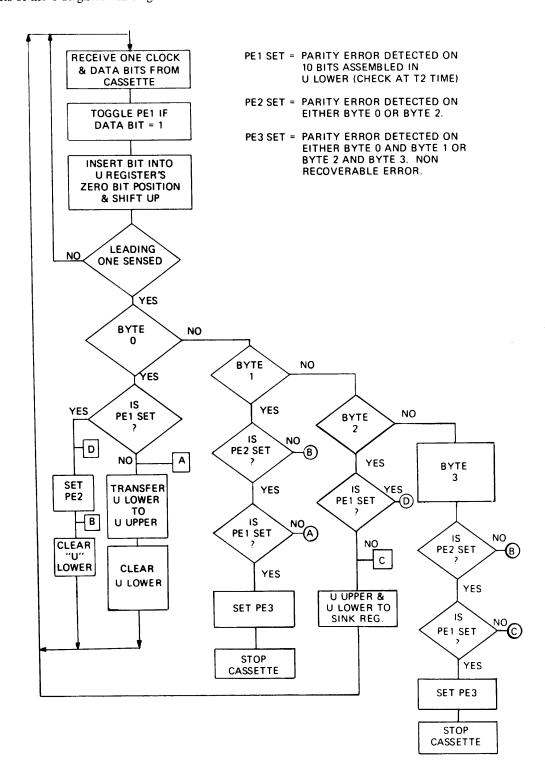

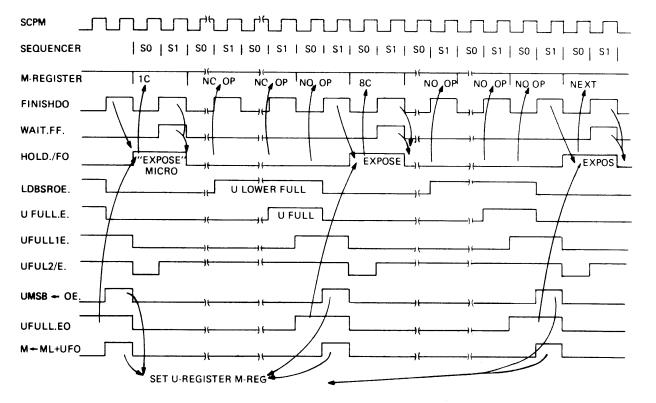

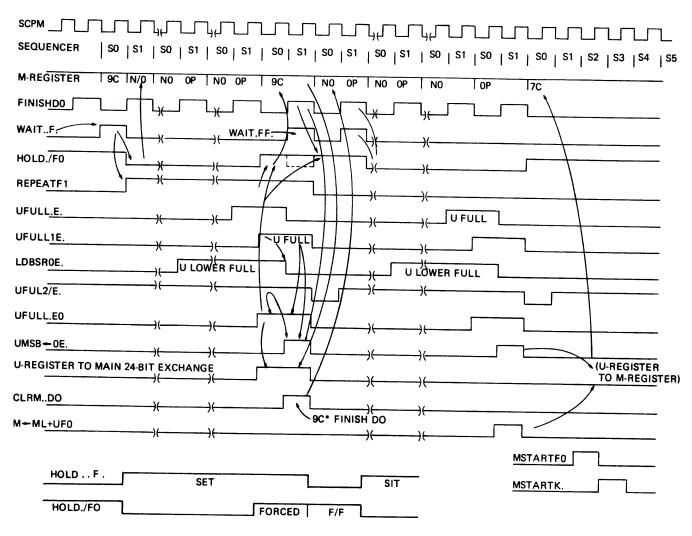

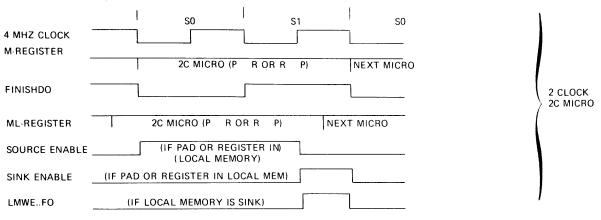

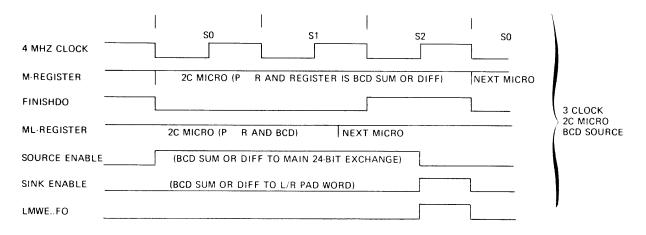

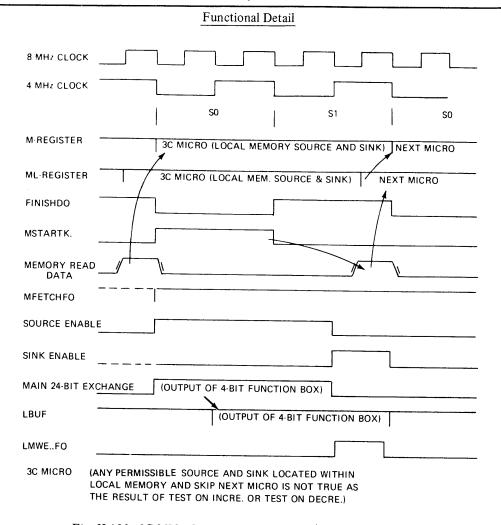

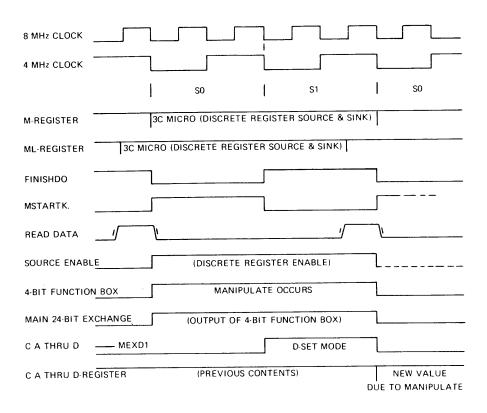

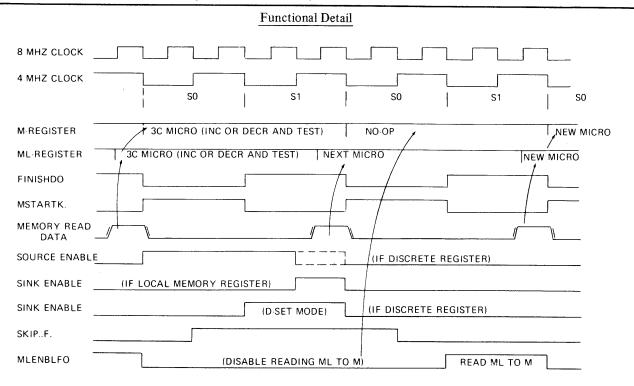

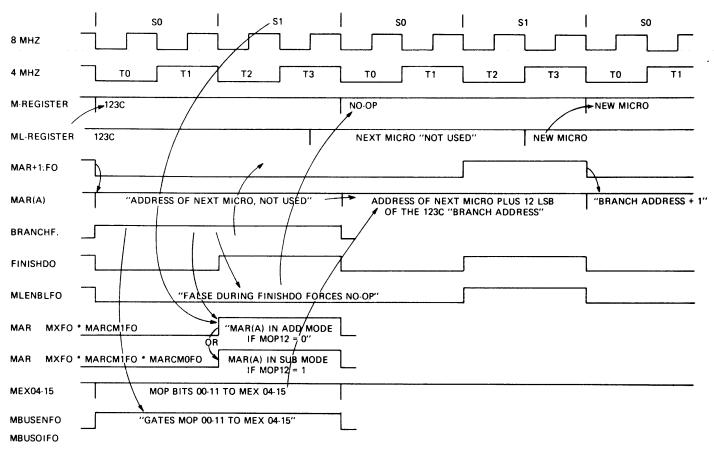

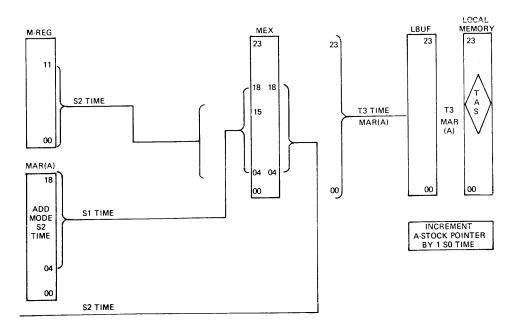

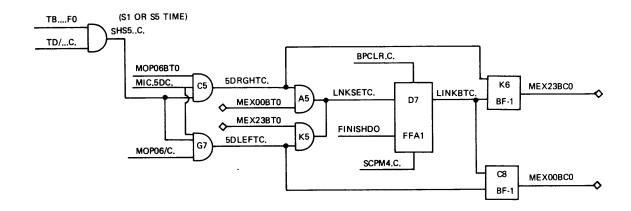

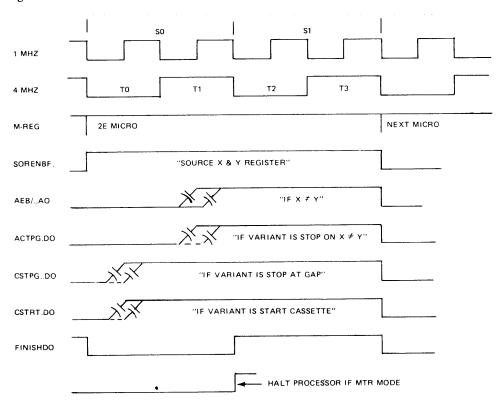

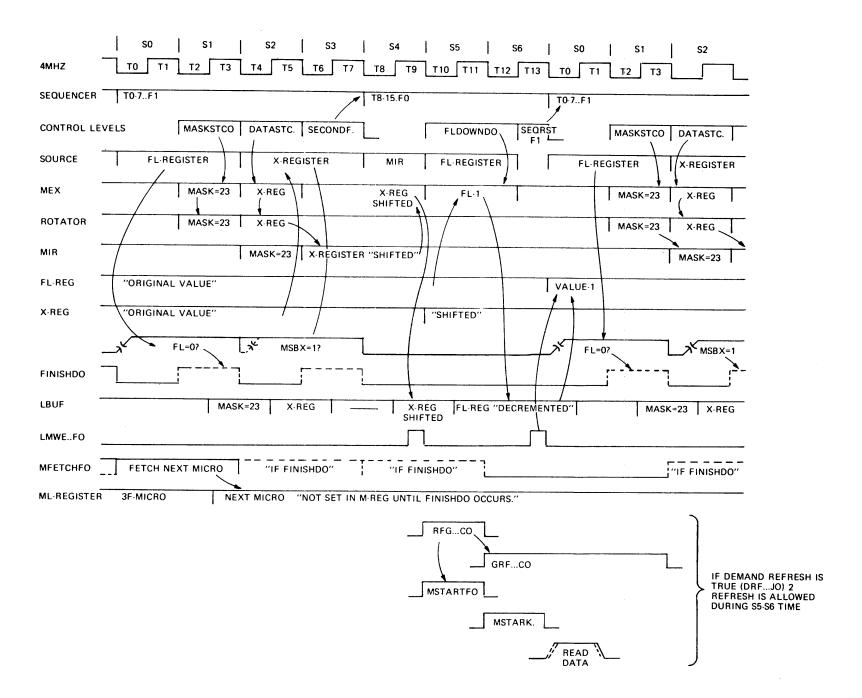

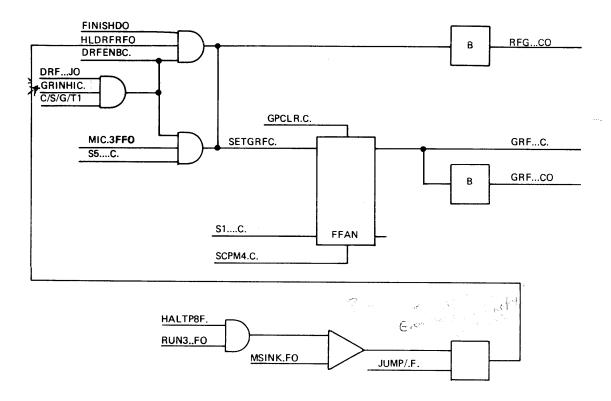

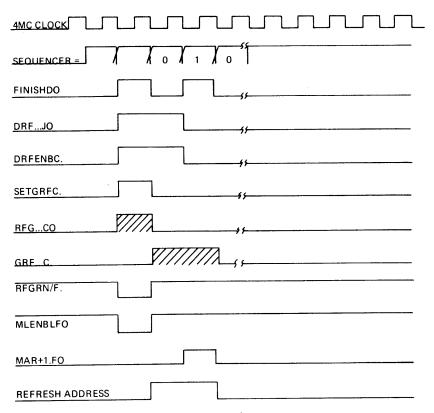

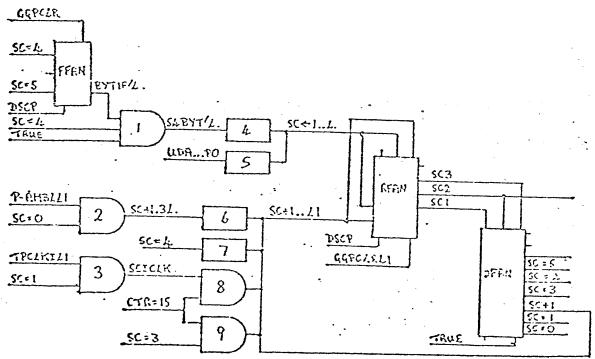

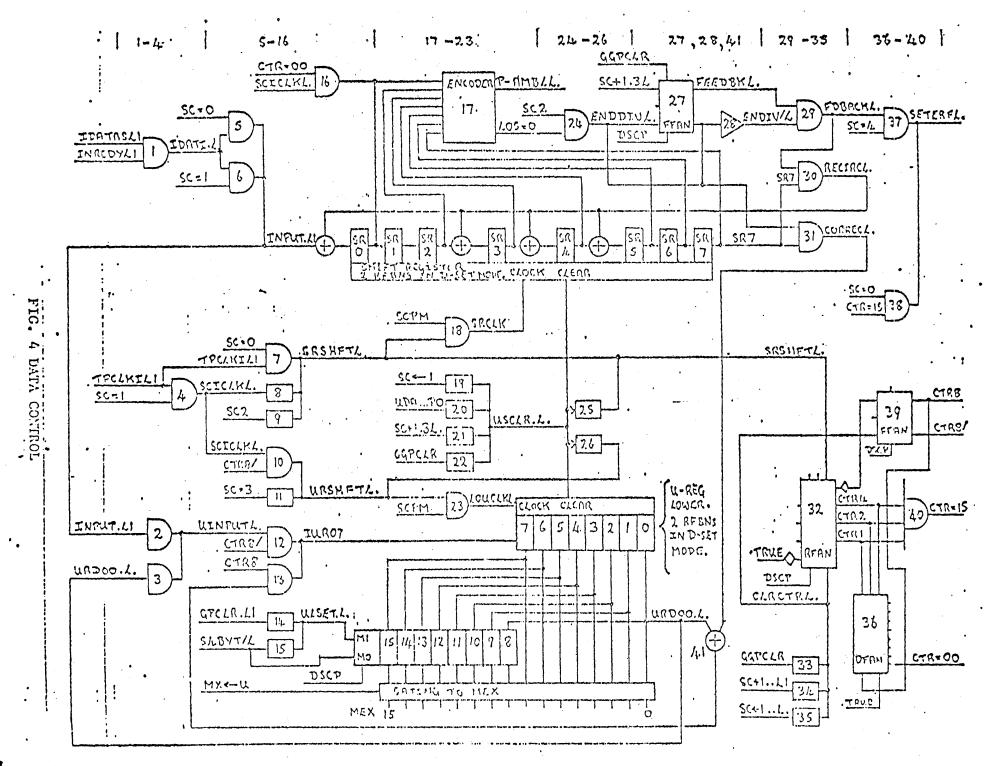

| FB Register                                    | FINISHDO 17                                      |

| FLCN Register (Field Length Condition 11       | FINISHDO Input Terms and Definitions 19          |

| L Register (Logic Register)                    | FINISHDO Logic                                   |

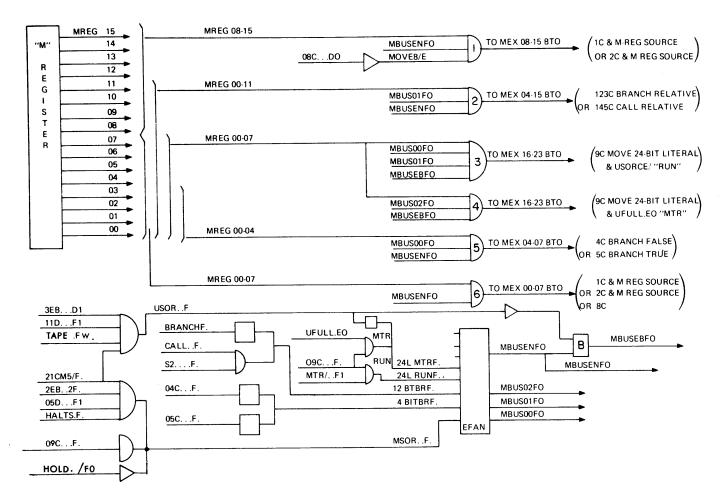

| M Register and Inputs (Micro Register) 8       | Four Bit Arithmetic and Combinatorial Section 73 |

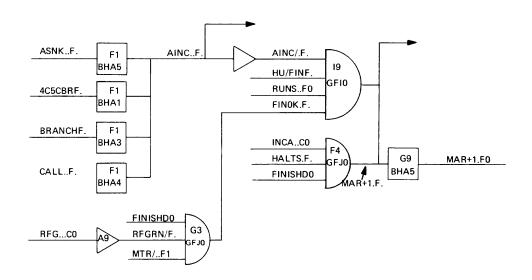

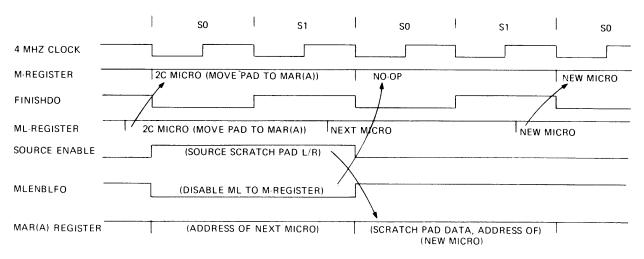

| MAR (A) Register                               | Generate and Propagate Terms                     |

| (Memory Address/Address Register) 8            | Introduction                                     |

| •                                              | Inverter                                         |

| MAXM Register  (Maximum M — Memory Register) 9 | Inverter Timing                                  |

| (1.14.14.14.14.14.14.14.14.14.14.14.14.14      | Local Memory                                     |

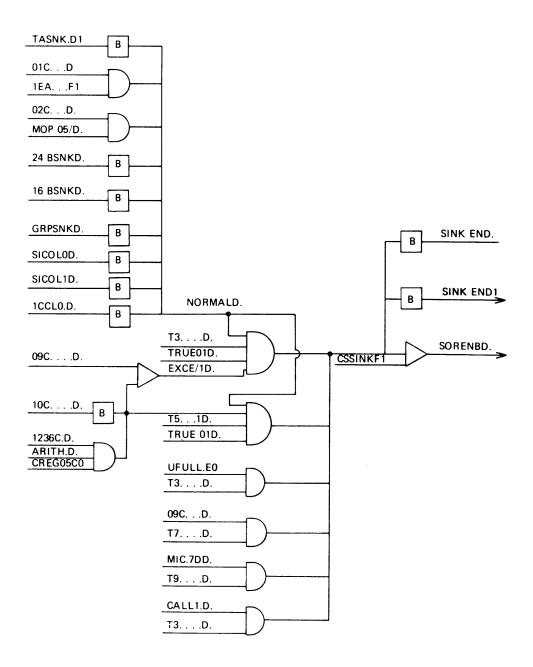

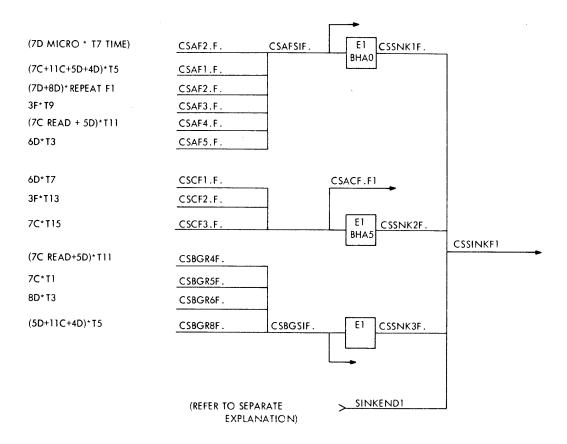

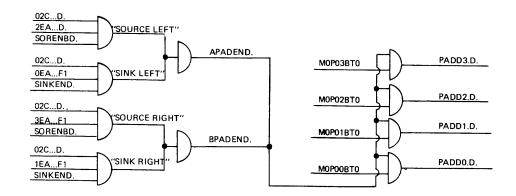

| MAXS Register                                  | Local Memory Source and Sink Enable              |

| (Maximum S – Memory Register) 8                | Local Memory Source and Sink Enable              |

| Memory Register and Associated Logic 12        | Input Terms 33                                   |

| Mull Register                                  |                                                  |

| Register Selection                             |                                                  |

| Scratchpad Memory                              | 8                                                |

| T Register (Transformer Register) 9            | Logic Timer                                      |

| TAS Register (Top of A Stack Register) 8       | Memory                                           |

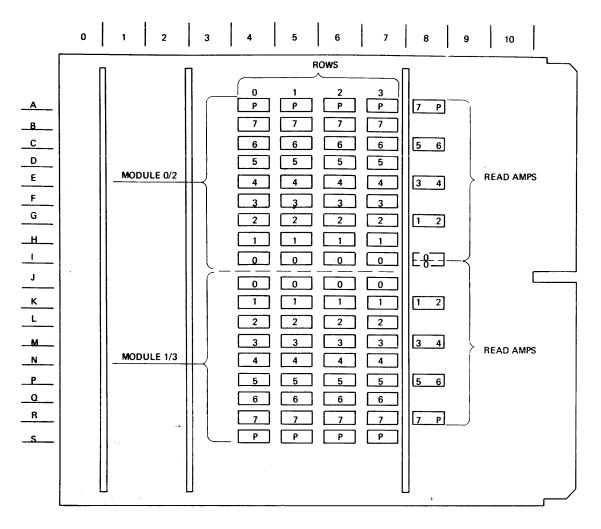

| U Register                                     | Storage Card                                     |

| X Register                                     | Storage Media                                    |

| Y Register                                     | Memory Addressing                                |

# INDEX (Continued)

| <u></u>                                            | Page No. |                                        |    |

|----------------------------------------------------|----------|----------------------------------------|----|

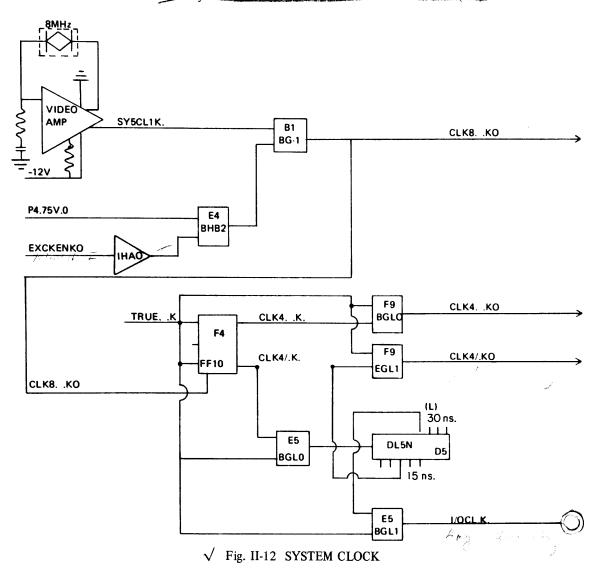

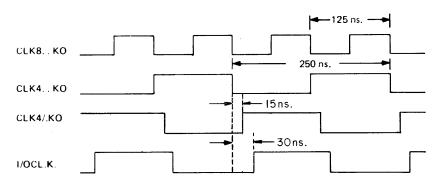

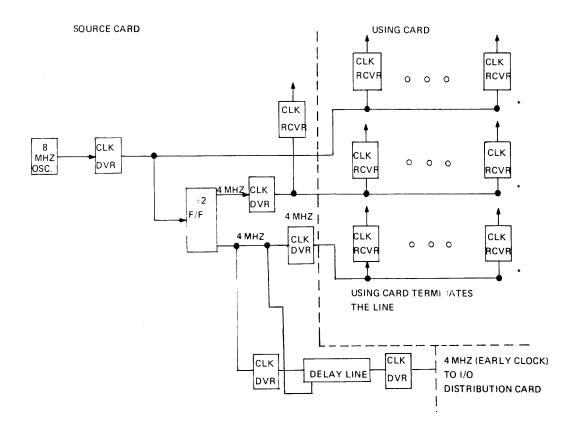

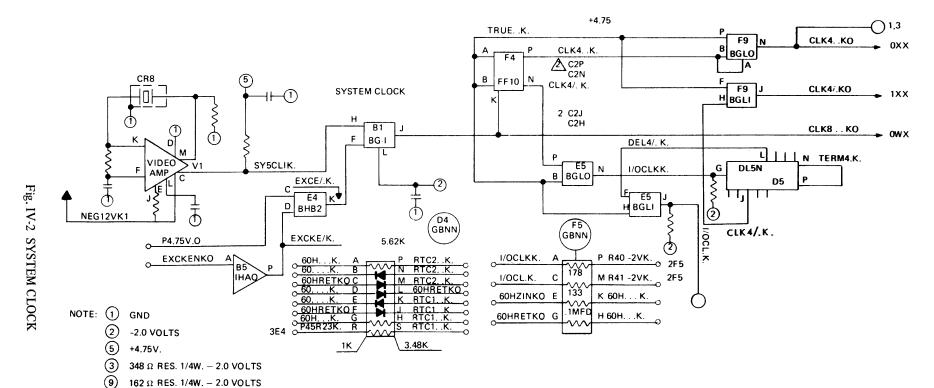

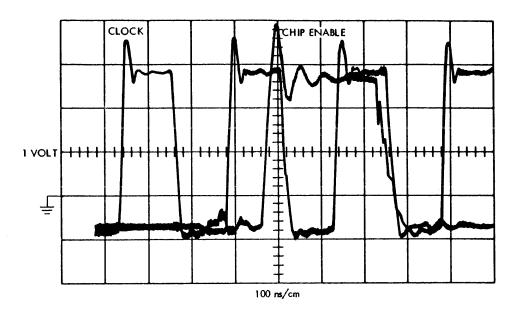

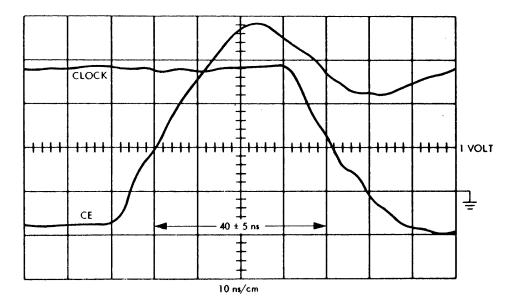

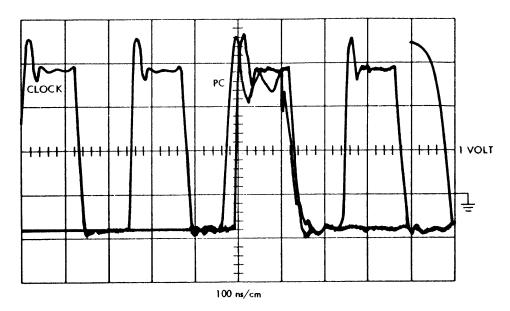

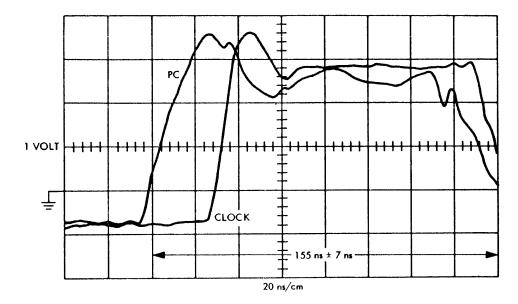

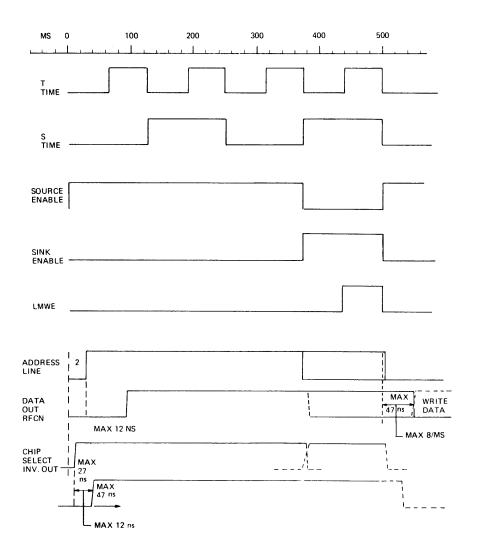

| Memory Address Register                            | 180      | Clock Distribution                     | 4  |

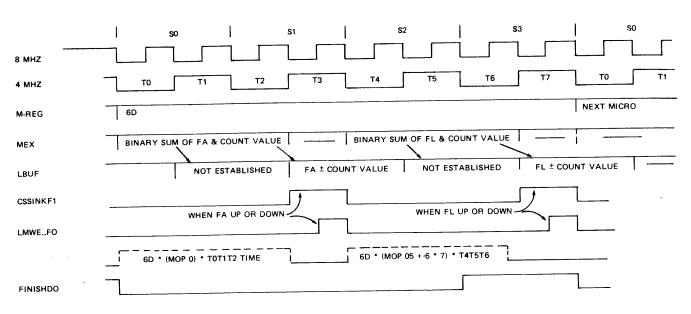

| Memory Base Timing                                 |          | Introduction                           | 1  |

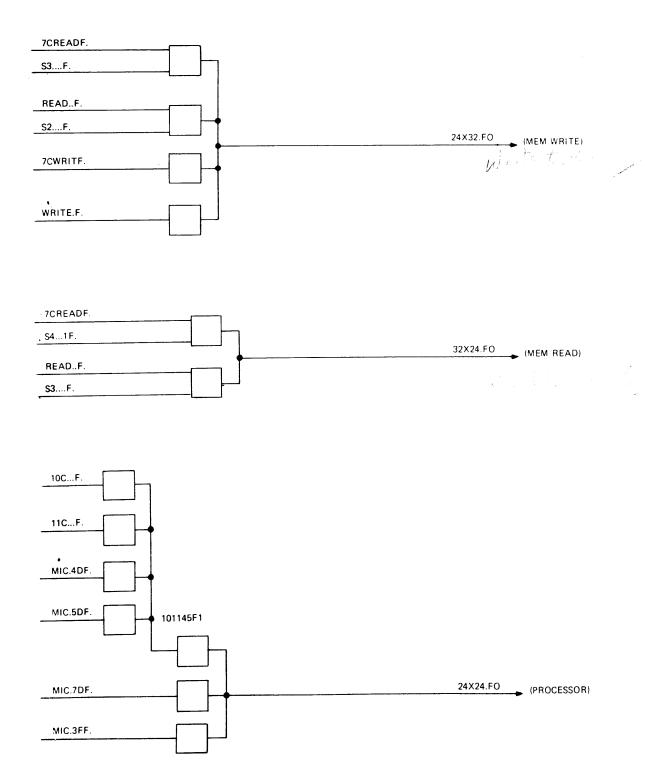

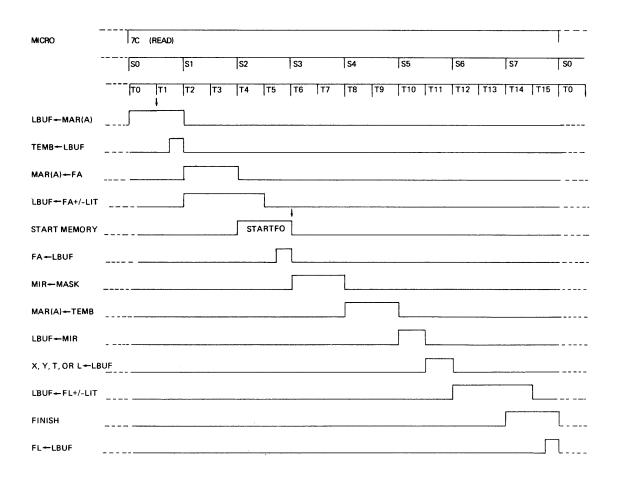

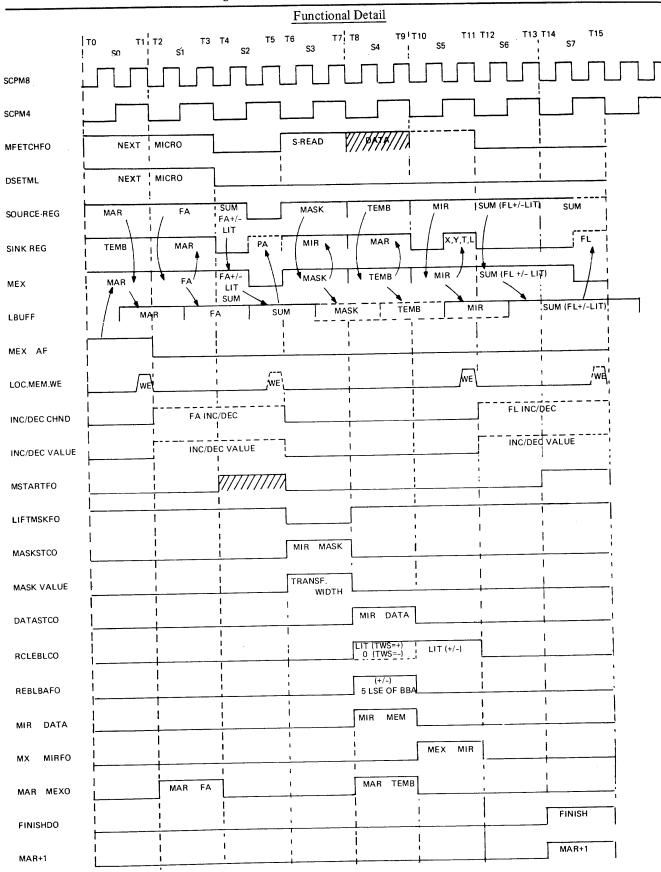

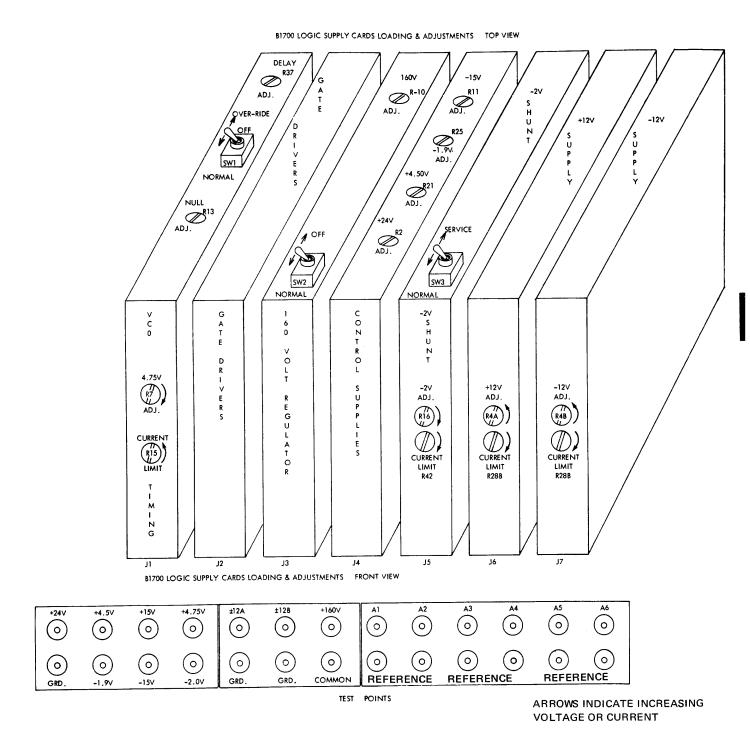

| Memory Data Flow (Read)                            |          | Memory Power Overvoltage Adjustment    | 29 |

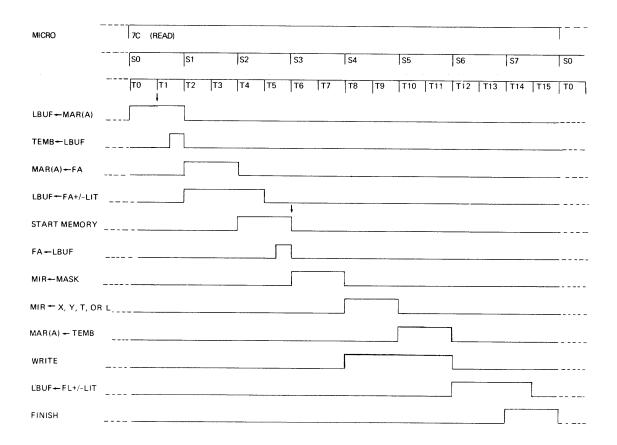

| Memory Data Flow (Write)                           | 193      | Memory Timing Adjustments              | 8  |

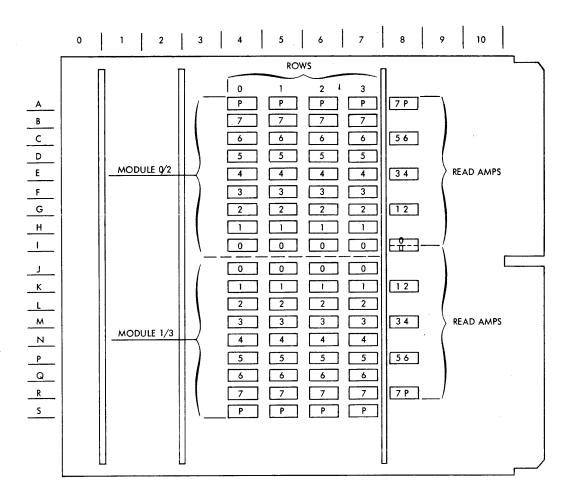

| Memory Group                                       | 174      | Memory Voltage Adjustment              | 30 |

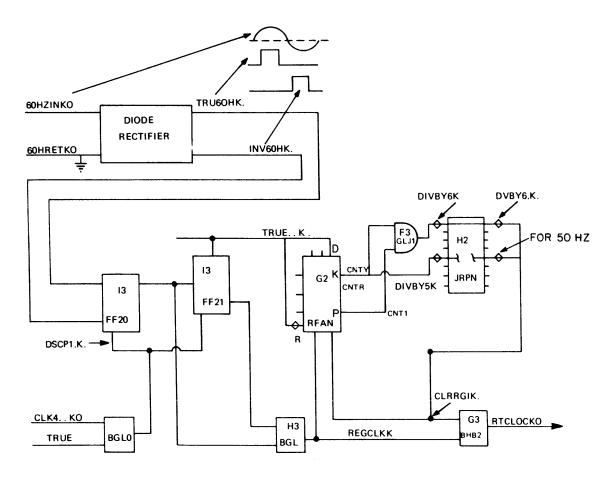

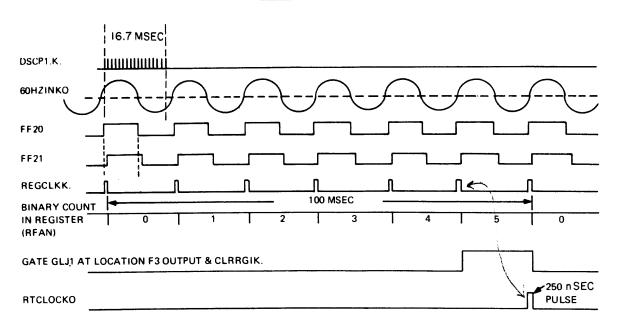

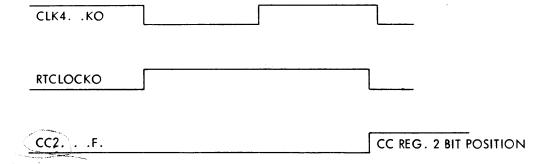

| Memory Information Register                        | 193      | Real Time Clock (RTCLOCKO)             | 4  |

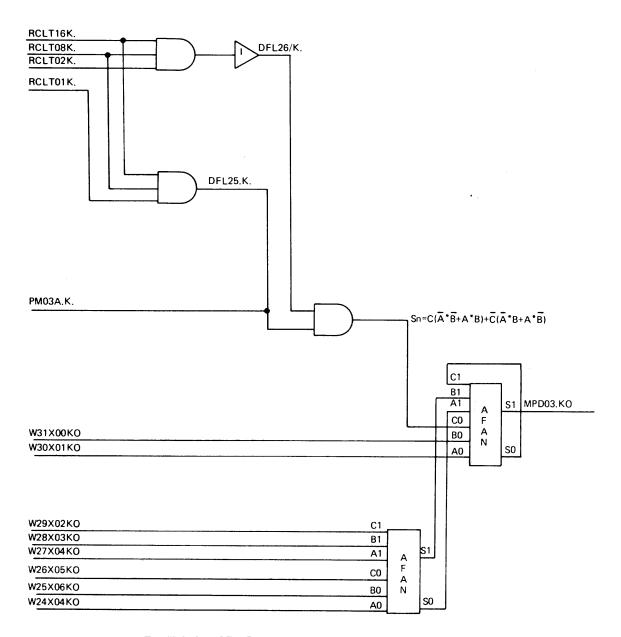

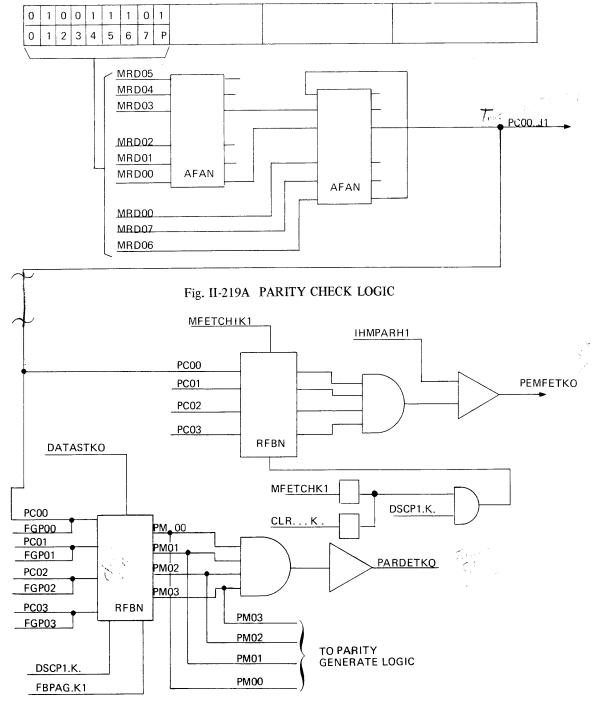

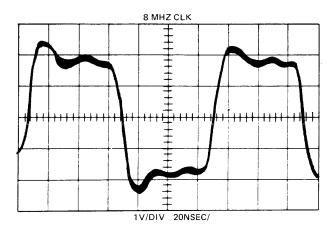

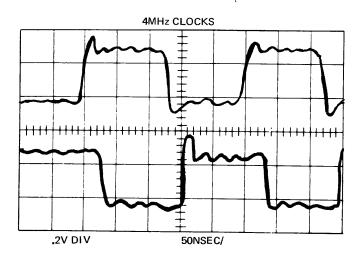

| Memory Parity Generation Logic                     |          | System Clock Check                     | 4  |

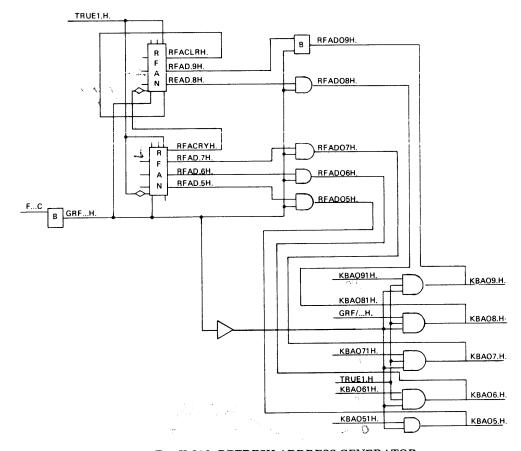

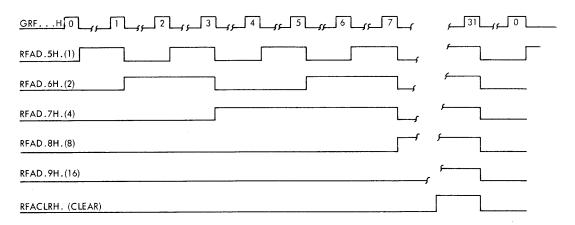

| Memory Refresh                                     | 185      | +19 Volt, Current Limit Calibration    | 31 |

| Memory Unit                                        | 174      | MAINTENANCE PROCEDURES - SECTION V     |    |

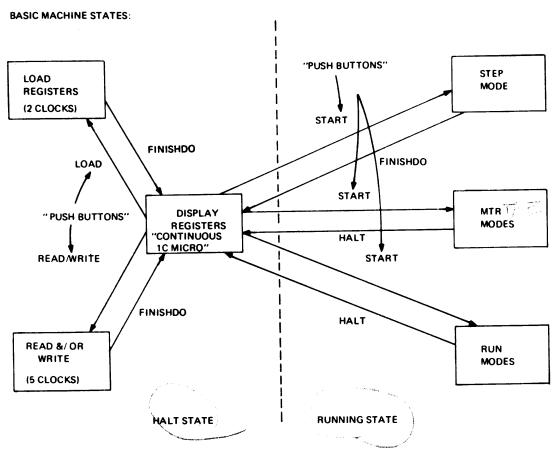

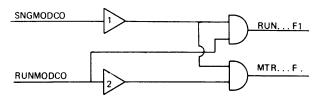

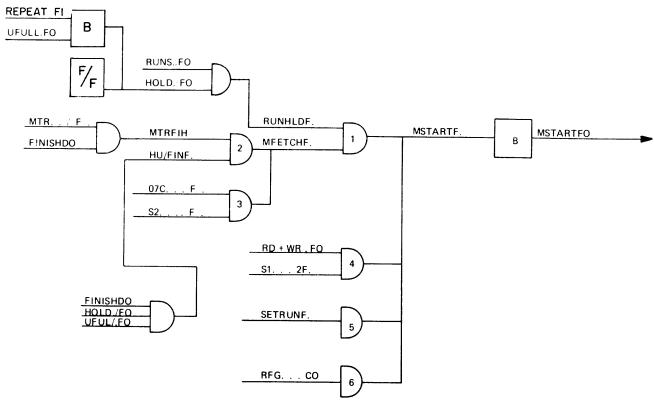

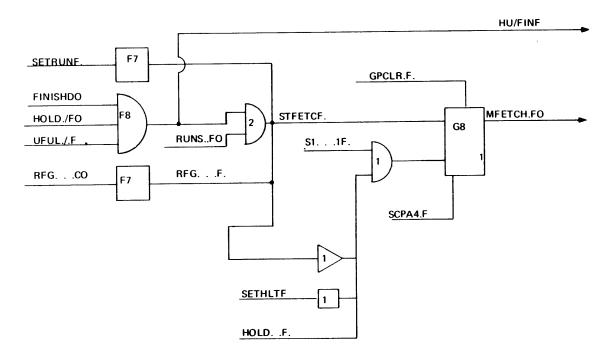

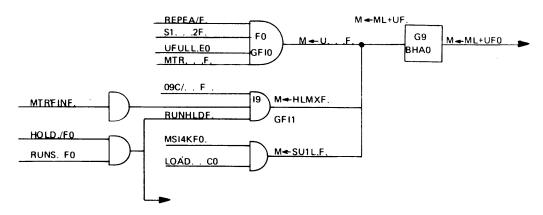

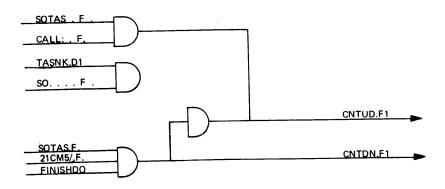

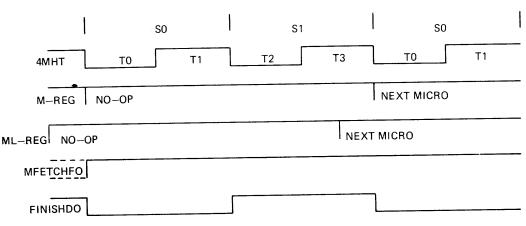

| Mode of Operation                                  | 15       | MAINTENANCE I ROCEDURES - SECTION V    |    |

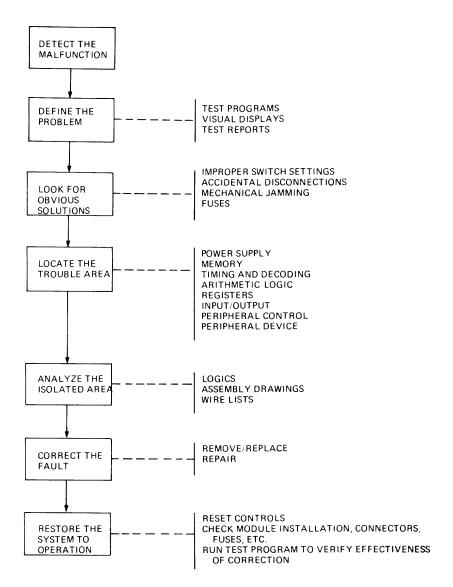

| Parity Check                                       |          | Introduction                           | 1  |

| Parity Logic                                       |          | B1700 Card Schematics                  | 10 |

| Processor – I/O Logic Interface                    |          | B1700 Logic Cards                      | 2  |

| Read Timing                                        | 49       | B1700 Memory Storage Cards             | 2  |

| Real Time Clock                                    | 9        | Card Installation                      | 10 |

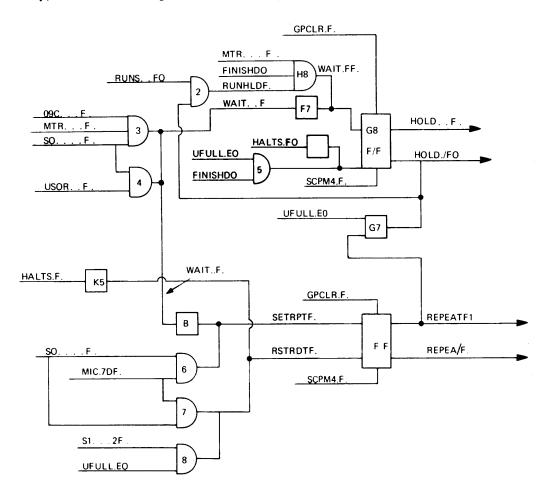

| Repeat and Hold F/F Input Terms                    |          | Integrated Chips                       | 7  |

| & Definitions                                      | 22       | Logic Diagrams                         | 2  |

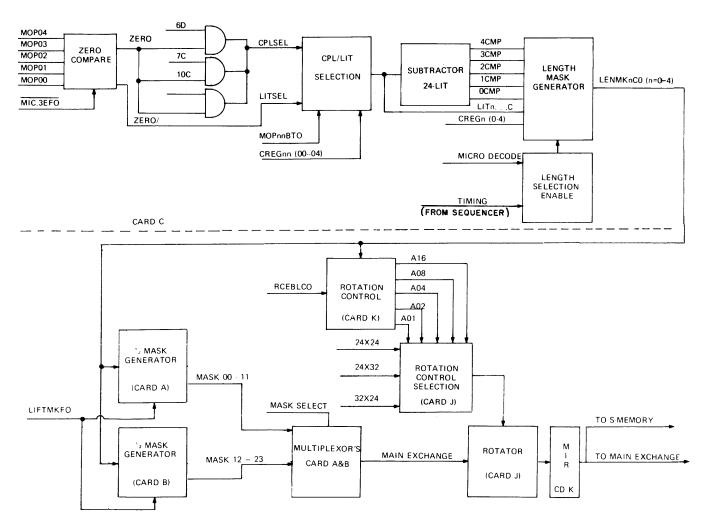

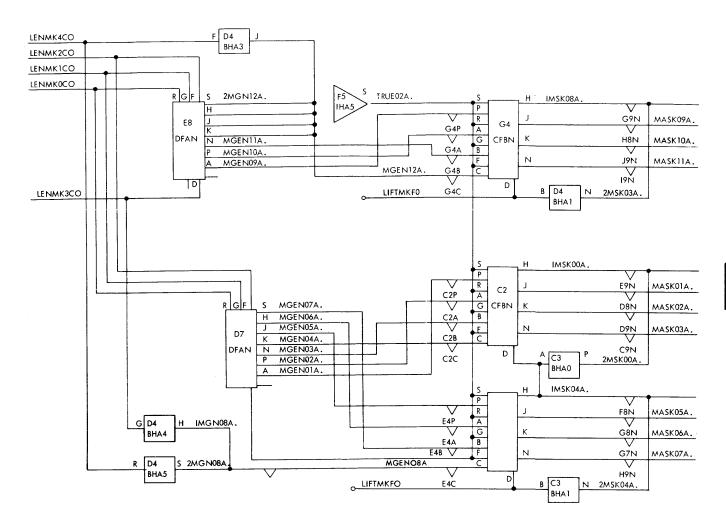

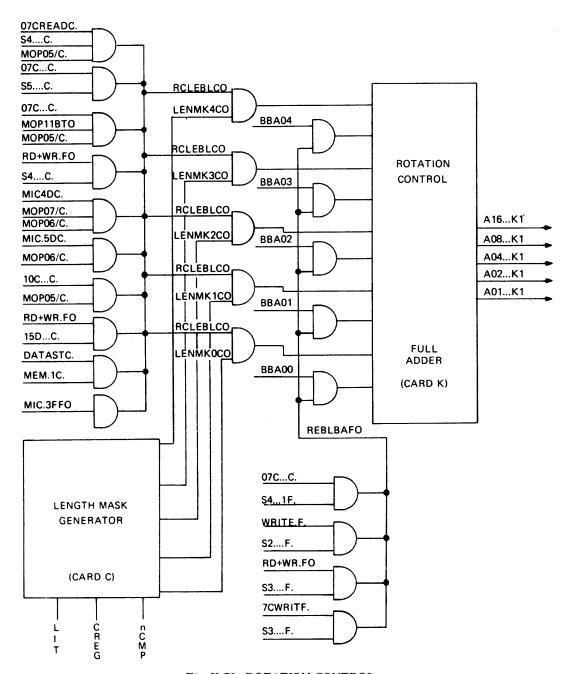

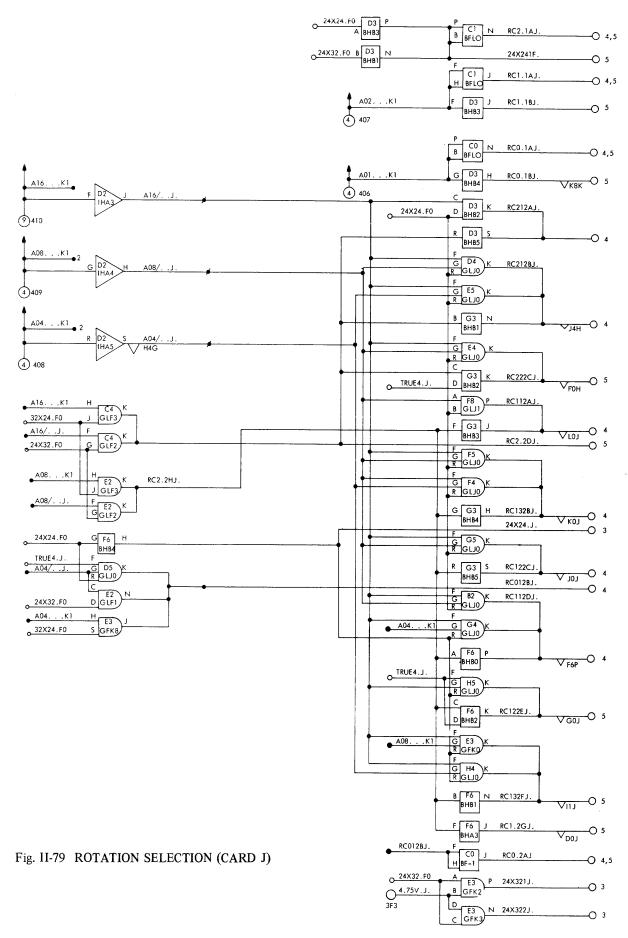

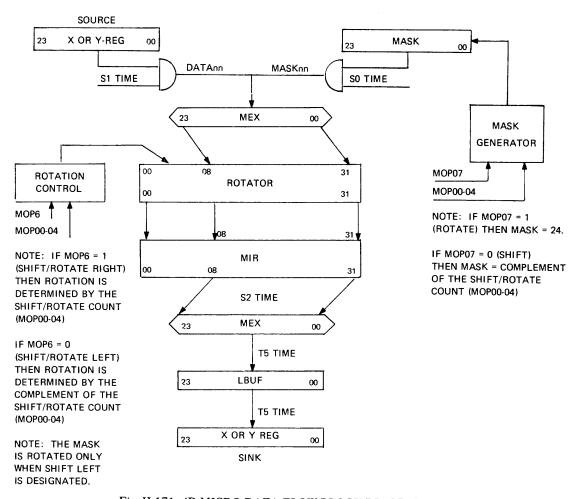

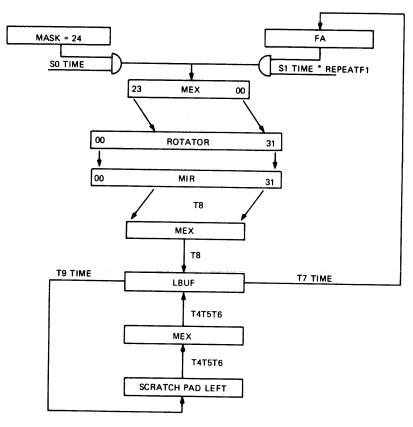

| Rotation Control and Control Selection             | 81       | Processor Maintenance Procedures       | 1  |

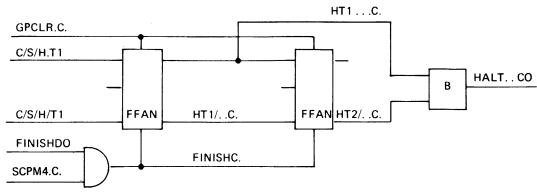

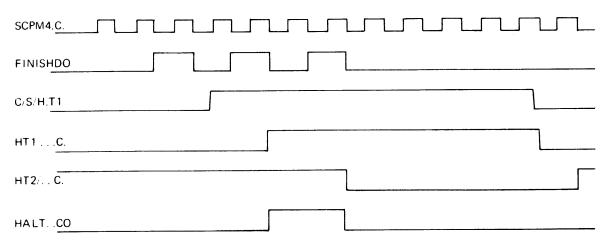

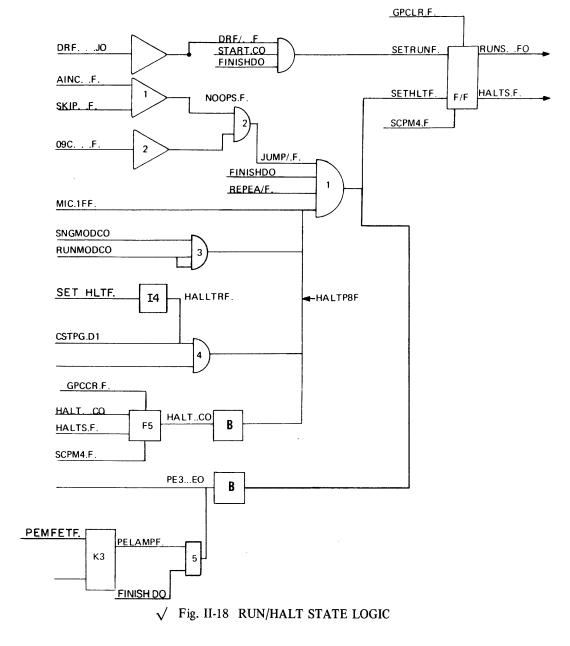

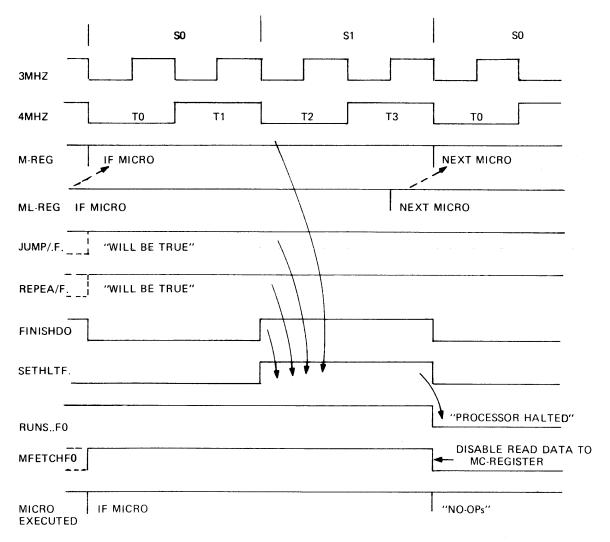

| Run/Halt Flip-flops                                | 13       | PSEUDO Connection System and Principle | 10 |

| Run/Halt Logic                                     | 13       | Maintenance Aids                       | 45 |

| Run State                                          | 13       | Memory                                 | 34 |

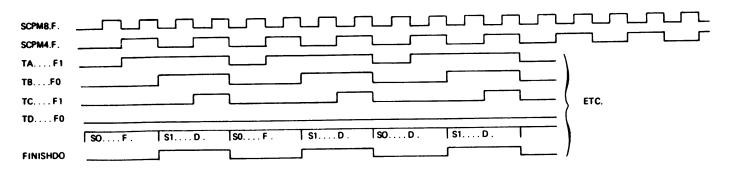

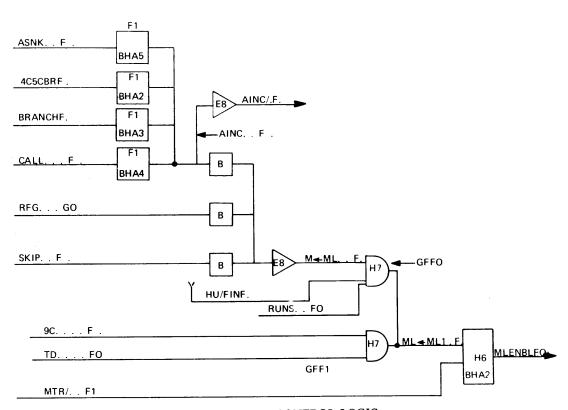

| Sequencer                                          | 16       | Memory Power Supply                    | 68 |

| $Sequencer-FINISHDO \dots \dots \dots \dots \dots$ | 19       | Memory Timing                          | 37 |

| Sequencer Logic                                    | 17       | Register Summary                       | 20 |

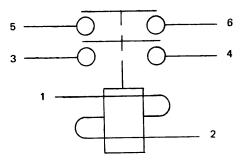

| S-Memory Processor Rotation Logic                  | 78       | Relays                                 | 53 |

| -12V D.C. Supply                                   |          | Power Supply                           | 42 |

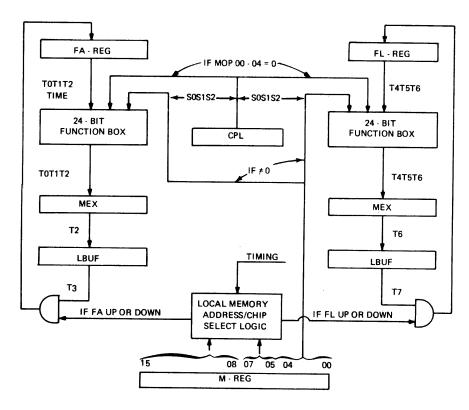

| 24 Bit Function Box Control                        |          | Troubleshooting Proecedures            |    |

| 24 Bit Function Box Introduction                   | 50       | 110 0010 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |    |

|                                                    |          | INSTALLATION PROCEDURES – SECTION VI   |    |

| CIRCUIT DETAIL – SECTION III                       |          |                                        |    |

| Constal Occalistan                                 | 1        | Expansion Kits                         | 9  |

| Crystal Oscellator                                 |          | Introduction                           | 1  |

| Introduction                                       | 1        | Memory Expansion                       | 9  |

| ADJUSTMENTS – SECTION IV                           |          |                                        |    |

| Adjustments Logic Power Supply                     | 31       |                                        |    |

| Central System Clock                               |          |                                        |    |

B 1700

**CENTRAL SYSTEM**

SECTION

INTRODUCTION AND OPERATION

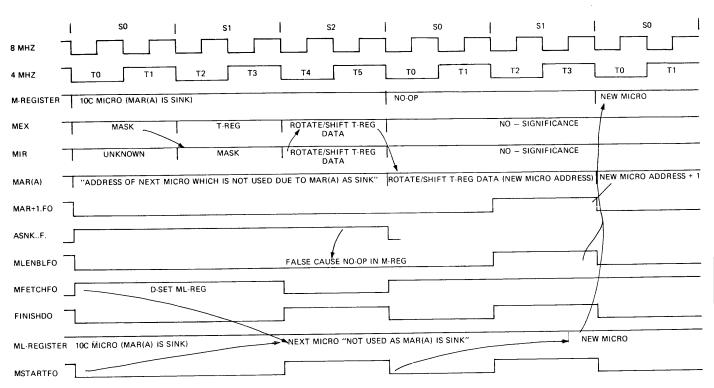

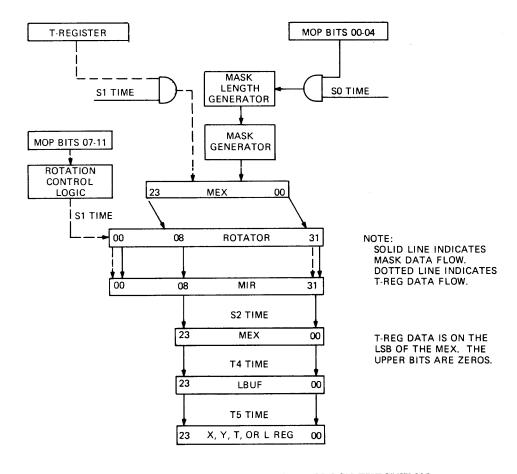

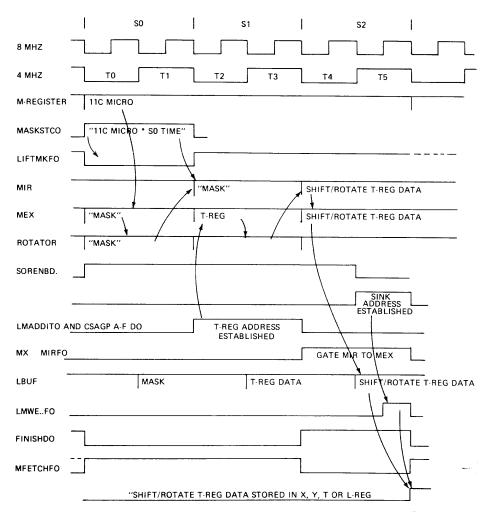

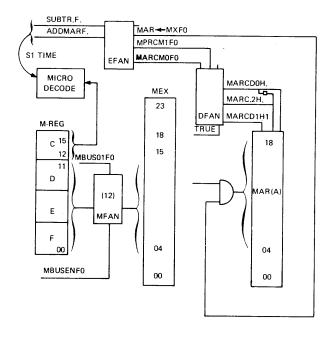

# Burroughs

FIELD ENGINEERING

# **TECHNICAL MANUAL**

# INTRODUCTION

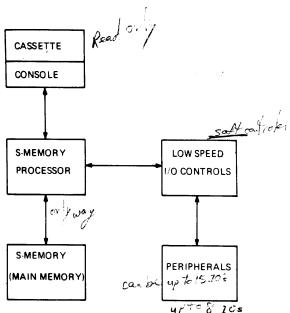

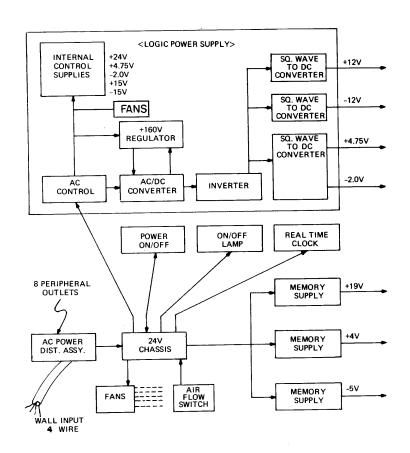

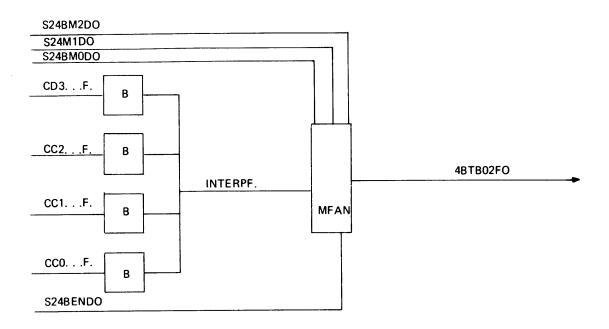

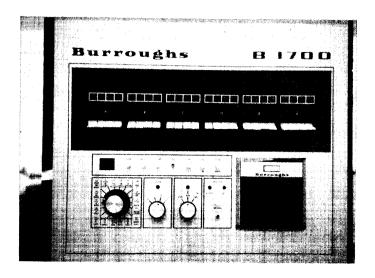

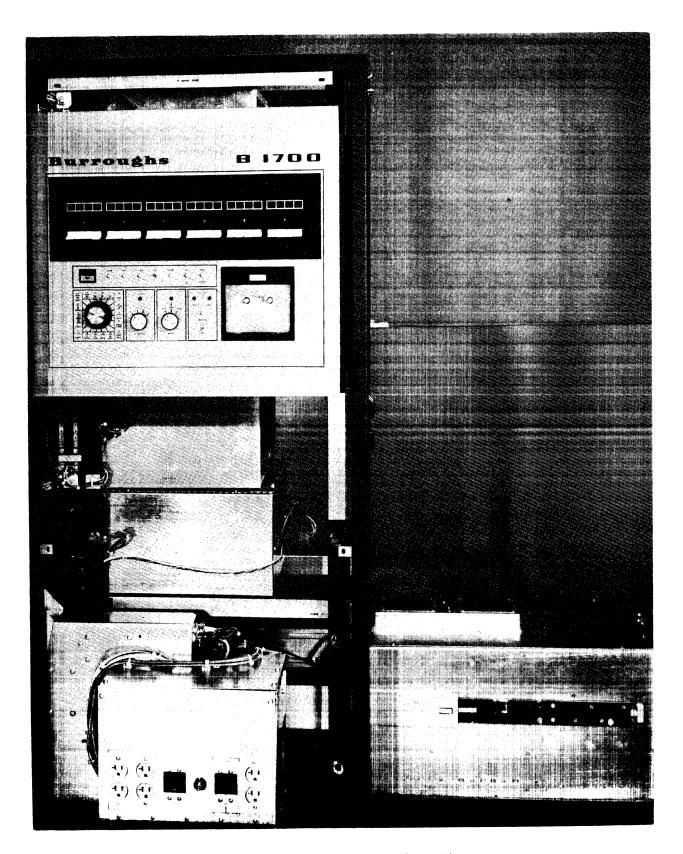

The B1700 System is a small scale data processing system used for general purpose data processing. The B1700 System contains an S-Memory Processor and a low speed I/O system. The S-Memory Processor, Memory and power supplies are described within this manual. The S-Memory Processor is a micro-programmed processor. Figure I-1 illustrates the B1700 System.

Fig. I-1 B1700 SYSTEM FUNCTIONAL BLOCK DIAGRAM

# MICRO INSTRUCTION

The B1700 Central System performs its operations by executing a set of low level (micro) instructions which are fetched and executed from the Main Memory of the system. There are approximately 25 of these micro instructions along with the associated logic sections, arithmetic sections, registers and pseudo registers required for performing a specific operation such as an add, data movement, I/O operations, etc. A micro instruction is hereby defined as the least amount of work an instruction could possibly perform within this system.

# MACRO INSTRUCTION.

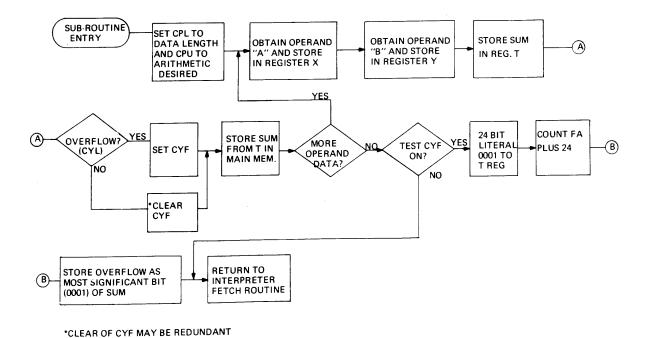

A "macro" instruction is the maximum amount of work which can be done by one instruction. In the B1700 these macro instructions are "built" by the programmer by using a series of micro instructions. An example of this would be an Add where a macro performs a complete add with storage of the sum and the detection of carries automatically. In the micro instruction set there is not an add instruction. The machine however, thru a series of micro instructions can perform an add operation and hence the add is "built" by the programmer.

# MICRO PROGRAMMING

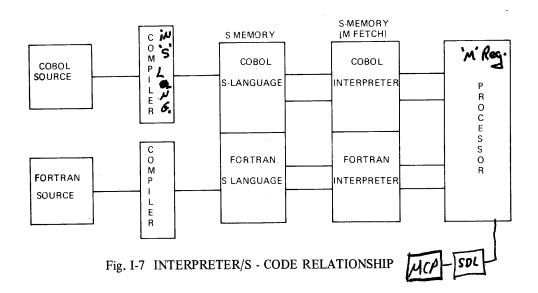

The micro programming of the B1700 or S-Memory Processor has several definite advantages. One advantage which is most obvious being ease in modification of the macro. That is, a macro can be changed through software rather than requiring a modification of the logic. The second obvious advantage is that micro programming allows the hardware to be "tailored" to the idiosyncrosies of a particular language such as COBOL, FORTRAN, etc.

# **B1700 CENTRAL SYSTEM**

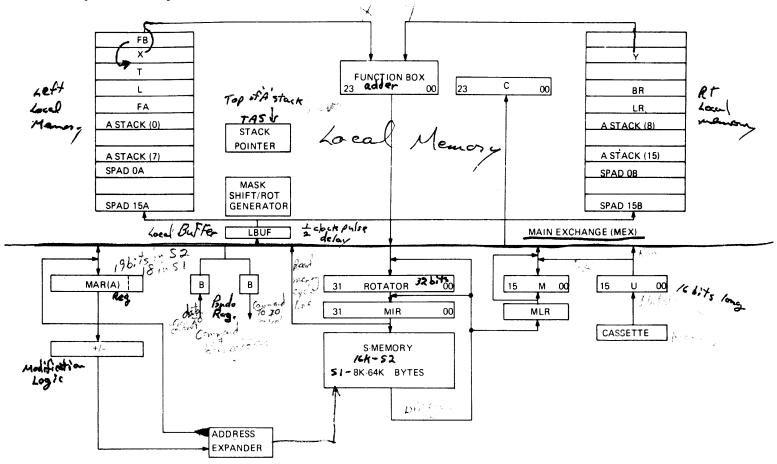

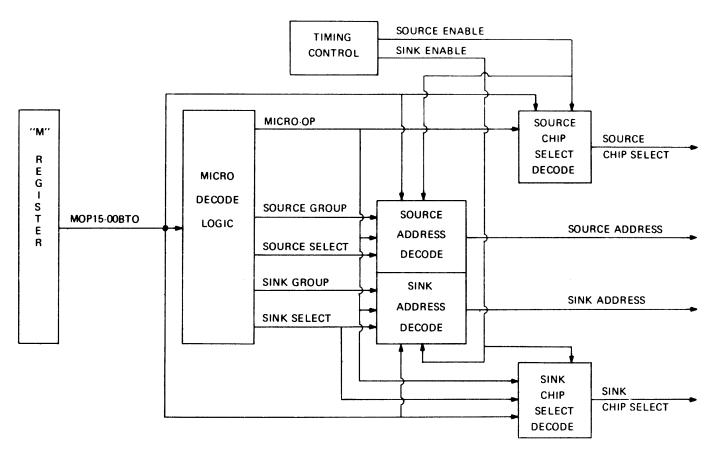

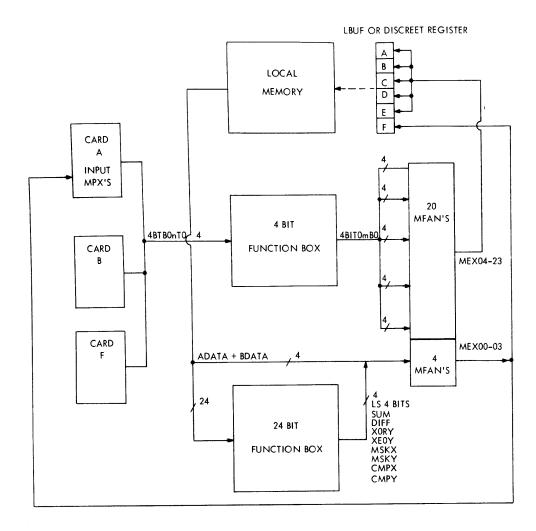

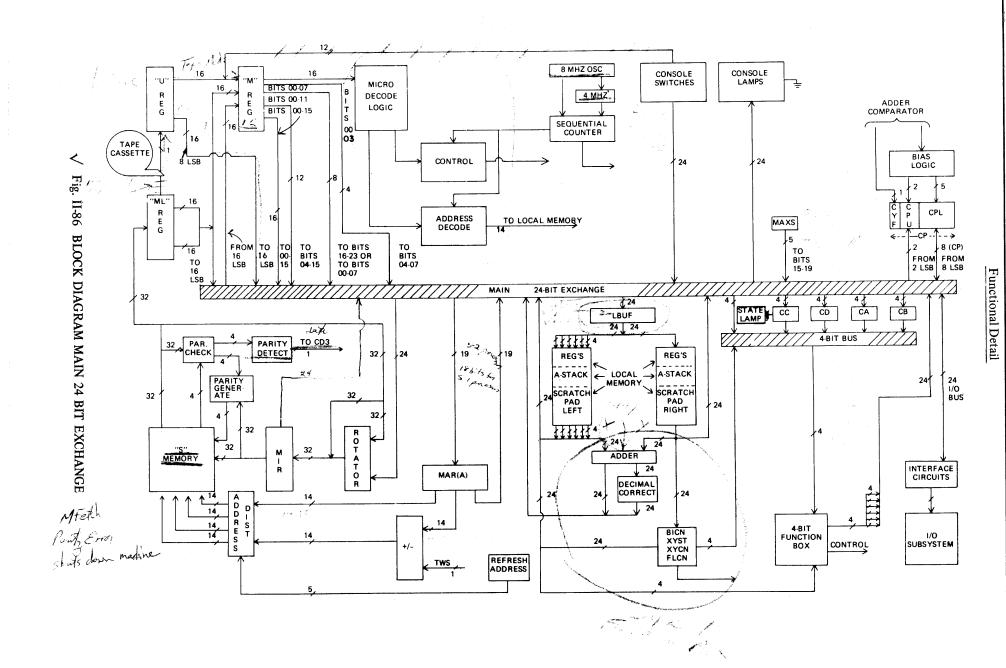

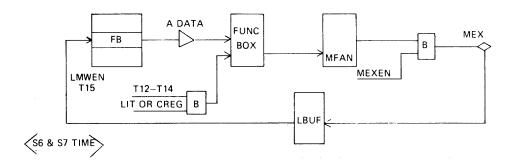

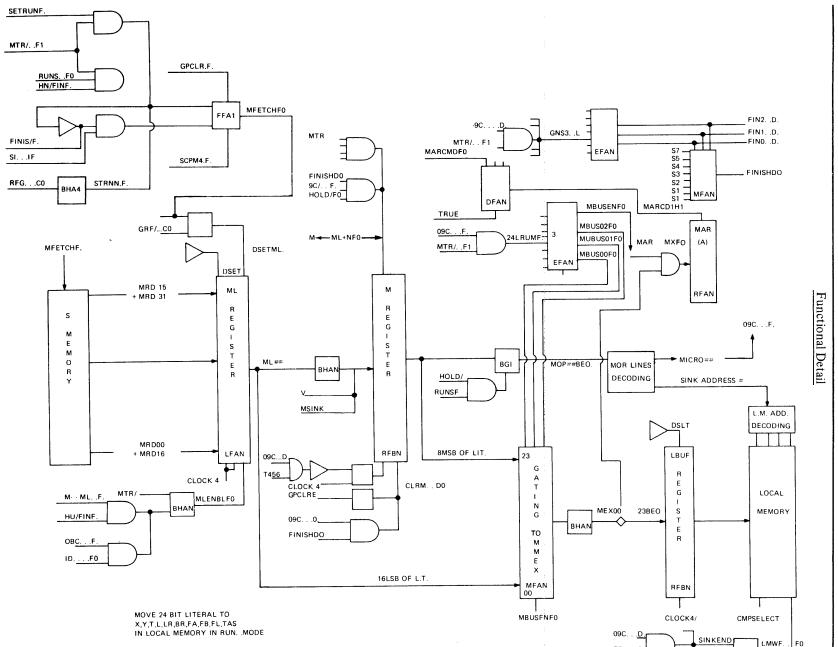

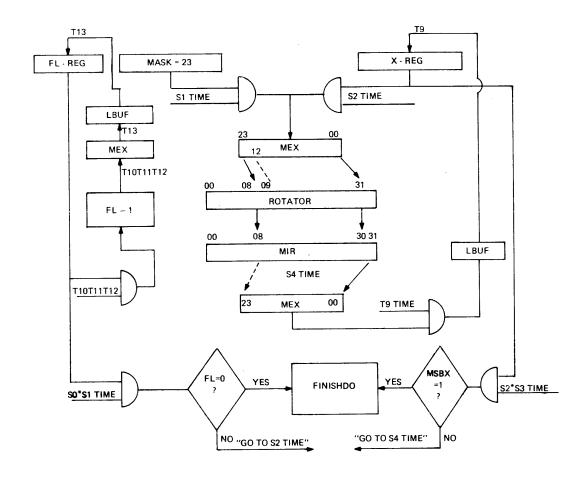

The B1700 Central System as previously discussed is a low level micro programmed processor and has been provided the necessary logic to perform the operations of a normal central processing unit. A basic block of the central system is shown in Figure I-2.

The B1700 System may be divided into the following functional areas:

Processor

Memory

I/O Sub-System

Power

Each of these areas are described generally within Section I of this manual. A detailed description is contained in Section II with the exception of the I/O Sub-System which is described in the B1700 System I/O Sub-System Technical Manual.

# **PROCESSOR**

# sect 5 p.19

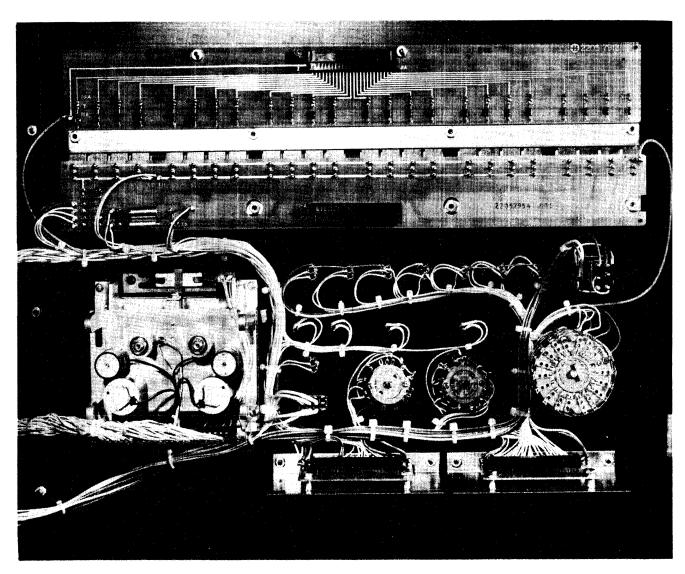

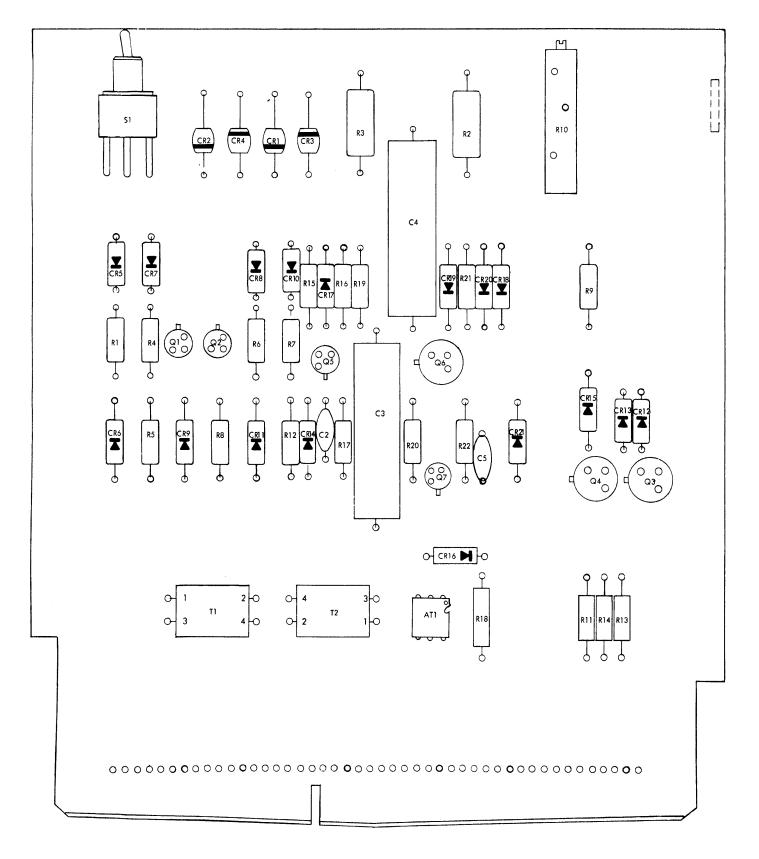

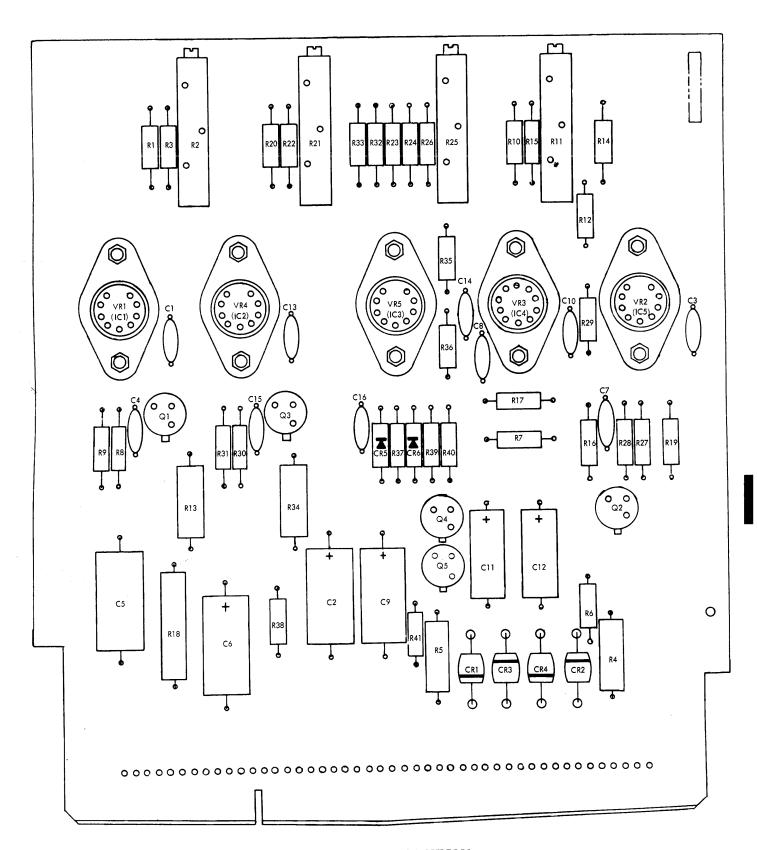

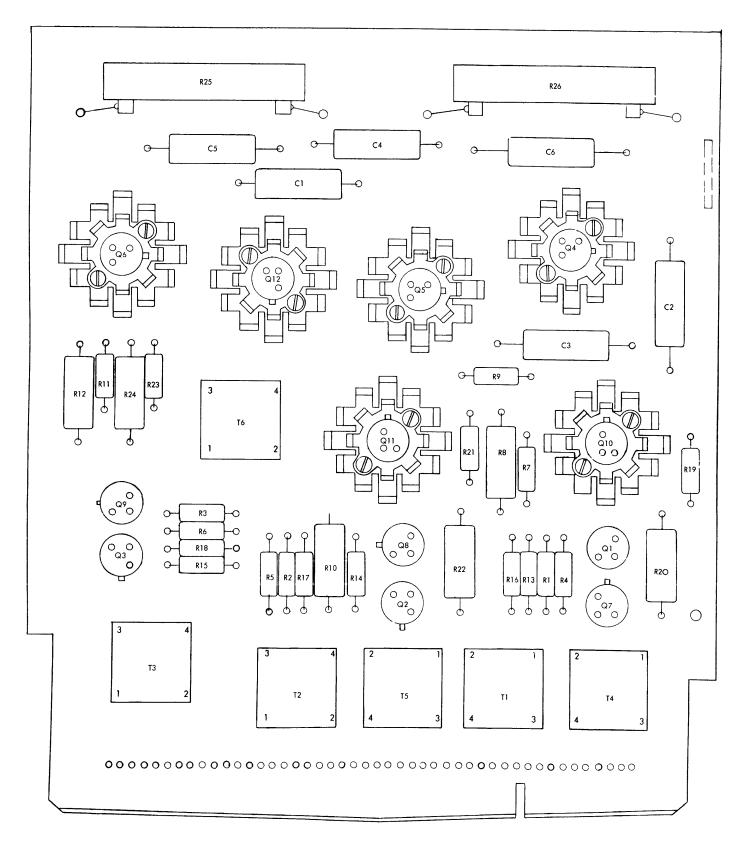

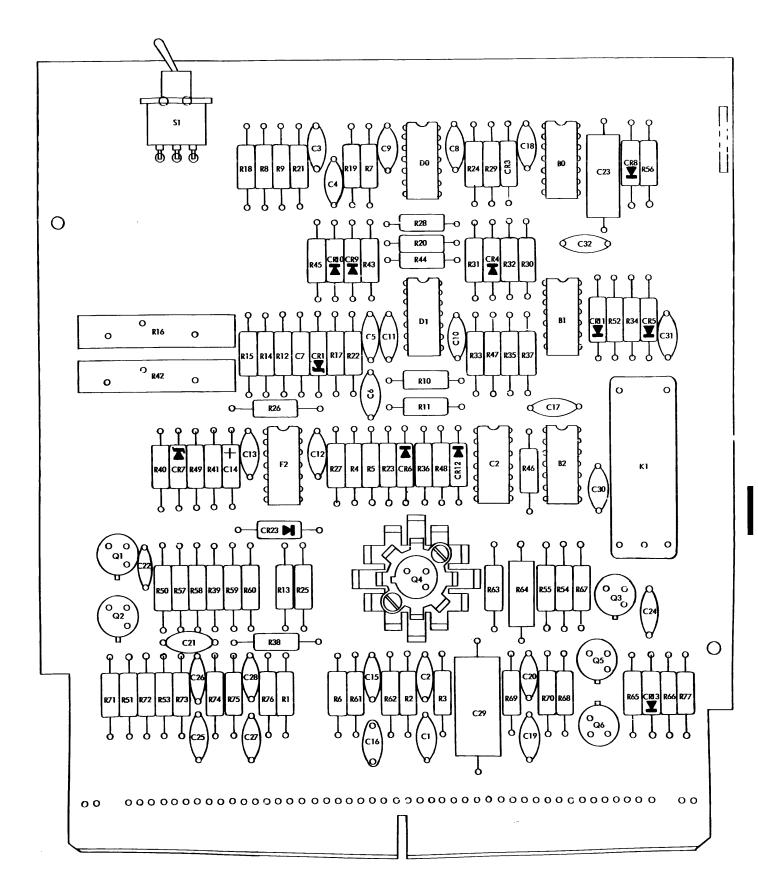

The S-Memory Processor, consisting of 9 logic cards, console and cassette loader contains the necessary logic to perform the arithmetic, logical and data movement/storage functions of a data processor. It also controls all I/O operations. The following is a list of the areas within the Processor and the Console with Cassette loader.

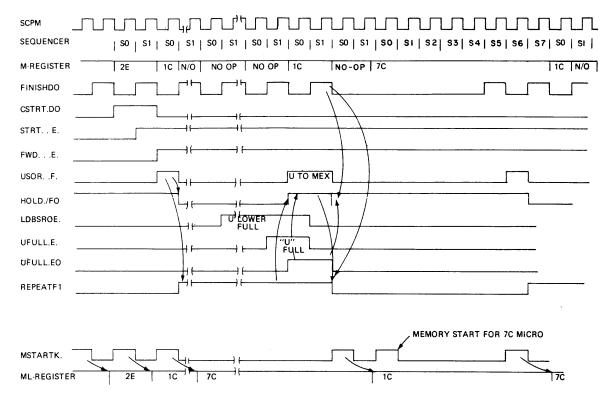

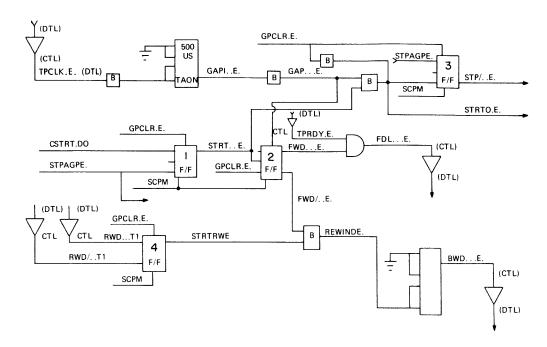

- 1. Cassette Tape Loader

- 2. Console

- 3. Main Exchange

- 4. Local Memory

- 5. 24-Bit Arithmetic and Combinatorial Unit

- 6. 4-Bit Arithmetic and Combinatorial Unit

- 7. Processor Registers

Figure I-2 is a basic block diagram of the processor and the following descriptions contain the basic functions of each of the seven portions of the processor listed.

Fig. I-2 BASIC BLOCK DIAGRAM

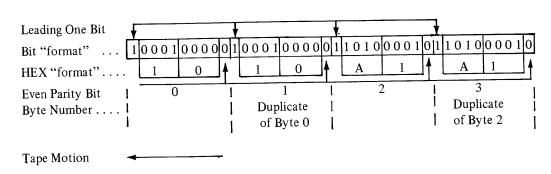

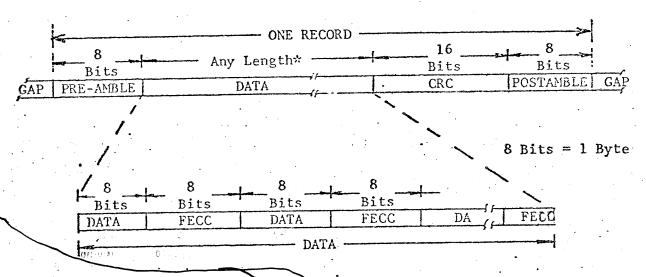

# CASSETTE TAPE

The C assette is physically located on the Console of the B1700 as shown in Figure I-3. The Cassette on the Console is a "read only" device, used for program loading and for storage of MTR/Diagnostic Routines which may be executed directly from the Cassette or entered in the Main Memory prior to execution. The physical characteristics of the Cassette are as follows:

Speed-10 ips (Inches per second)

Density 800 BPI (Bits per inch)

Tape Length-300 ft.

Data Format-Bit Serial/8 bits per character

For a detailed description of the Cassette and format used on entering micros via the Cassette refer to Section II.

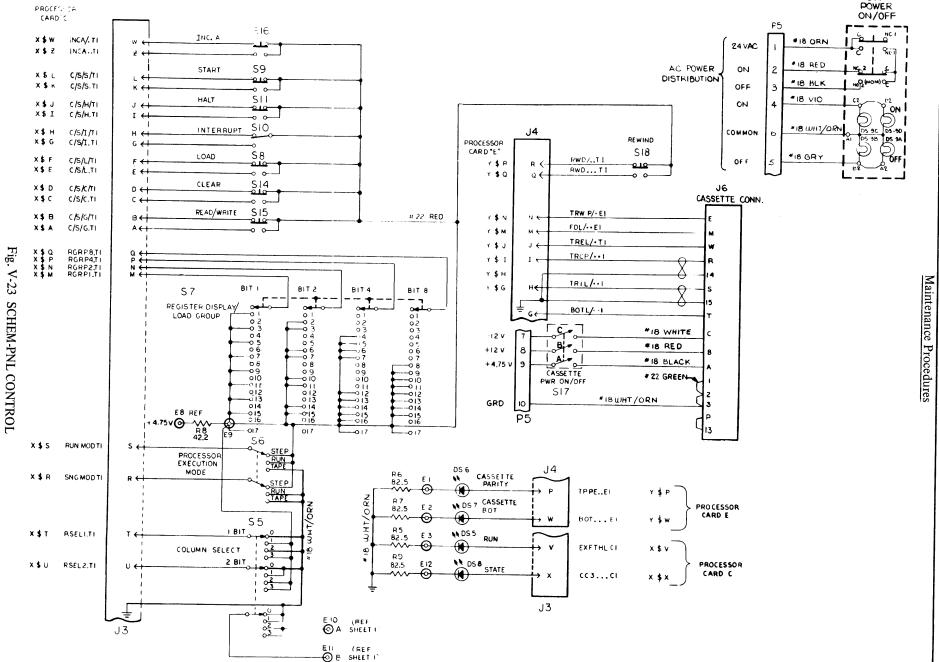

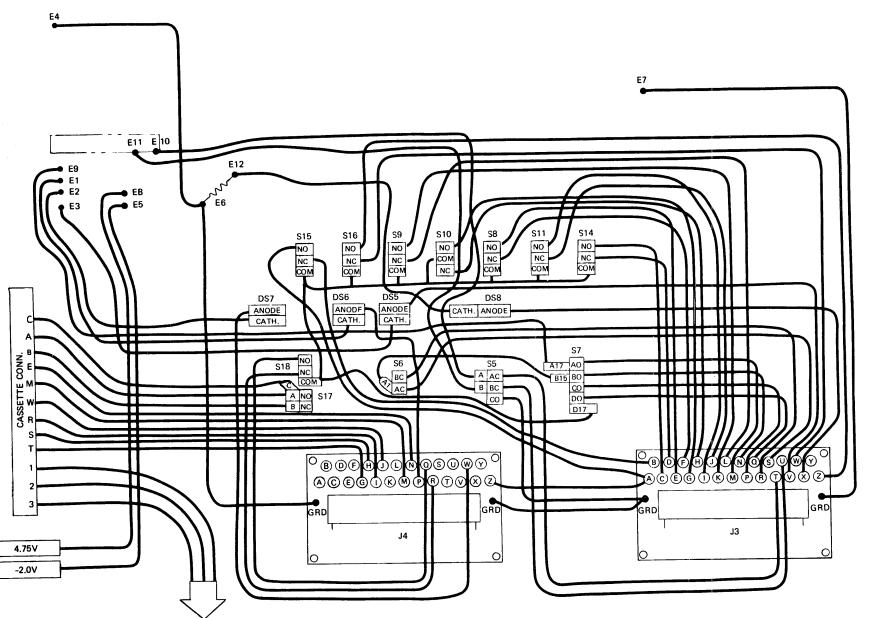

# **CONSOLE**

The Console of the B1700 is used for displaying/entering data of various registers within the S-Memory Processor. Data also may be loaded into memory from the console. The console may also be used to display memory data. The Console contains a mode switch to place the machine in the RUN/STEP/TAPE mode of operation. As previously described, the Cassette is a part of the Console and therefore, the Console contains the necessary switches/lamps for operation of the Cassette. Refer to Figure I-4.

Fig. I-3

Hex

Burroughs

Burroughs

Software Billon

AEAD ONLY

AEAD ONLY

Fig. I-4

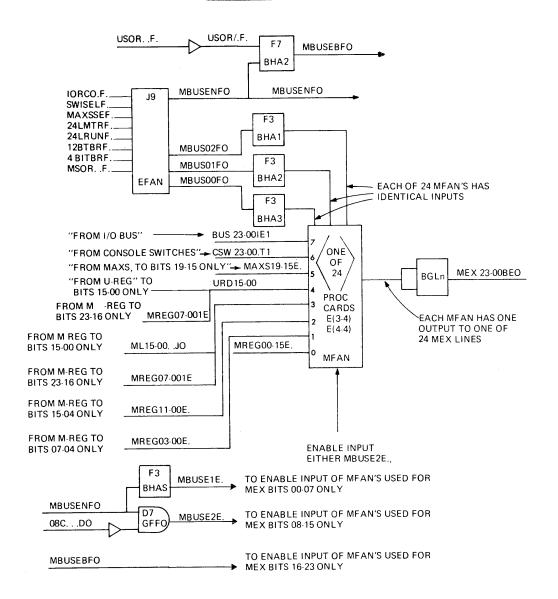

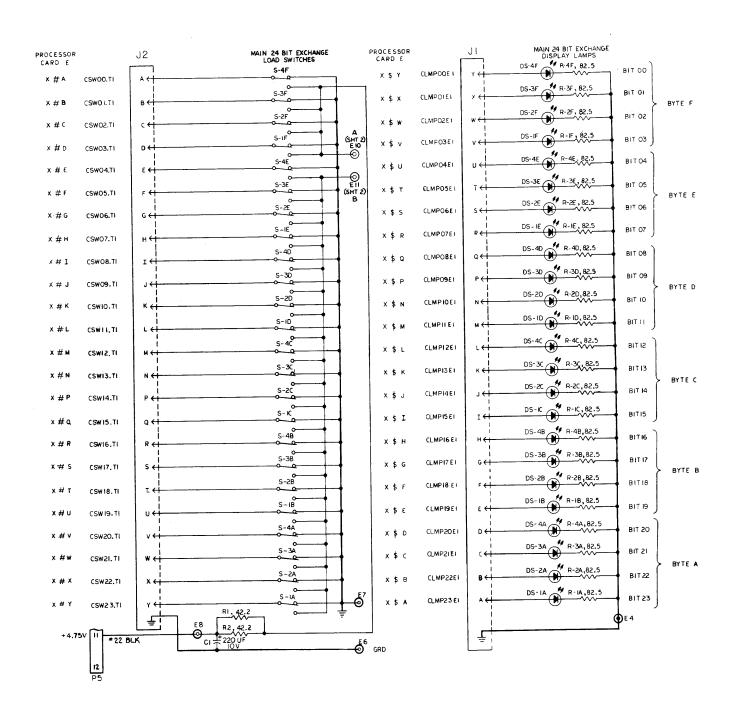

# MAIN EXCHANGE (MEX)

The Main Exchange is the main bus within the processor. It is used for movement of data within the processor and is 24 bits wide. It is also used to transfer 4 bit data from source to destination in addition to the normal 24 bit word.

The Main Exchange, when the machine is halted, receives data from the register selected by the console switches and this data is automatically displayed on the console lamps. If the load button is depressed when the processor is halted, the contents of the console switches will be placed on the Main Exchange and subsequently loaded into the register which has been previously selected.

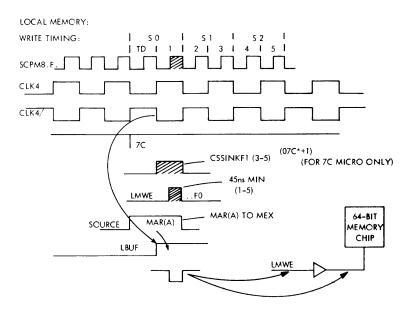

# LOCAL MEMORY

The Local Memory is that part of the machine where the majority of the registers reside. Several registers such as the C Register and MAR (A) have been made discreet because they must always be present for operations whereas if they were located in the Local Memory they would not be available for the controlling functions which they must provide. Each of these registers and micros which affect these registers are described in Section I.

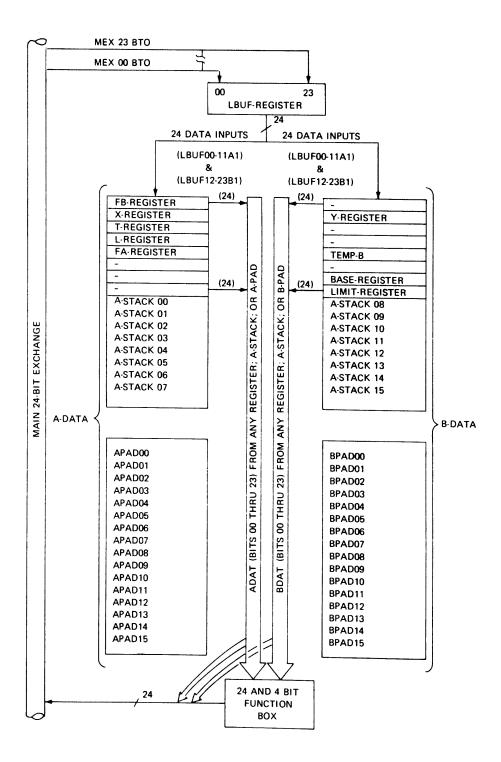

Local Memory is divided into three main sections of logic; LBUF, Left (A) Half, and Right (B) half. The following is a brief description of each section and its contents:

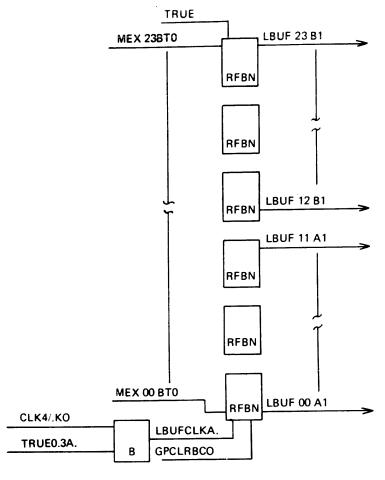

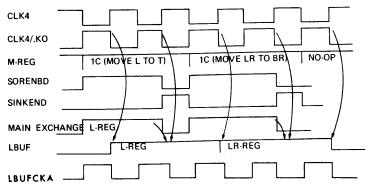

A. LBUF

LBUF is the input to the Local Memory and receives its input from the Main Exchange. LBUF is 24 bits in width and is used to hold the data to be written into local memory for an additional half clock period to allow the local memory write logic to complete the write operation.

B. Left (A) Half

Left Half of the local memory or sometimes referred to as "A" Half contains the following 4, 16, and 24-bit registers:

$$\begin{array}{ccc} Registers - FB & X \\ & L \\ & T \\ & FA \end{array}$$

(Note that FA, FB, L, and T may be divided into other registers)

In addition to the above mentioned register, Left Half of Local Memory contains words zero through seven of "A" Stack and words zero through fifteen of Left Scratchpad.

C. Right (B) Half

The Right Half sometimes referred to as "B" Half of Local Memory contains only 24 bit registers in addition to words eight through fifteen of "A" Stack and words zero through fifteen of Right Scratchpad. The following are the 24 bit registers located in Right Half of Local Memory:

Registers -Y

**TEMPB**

BR

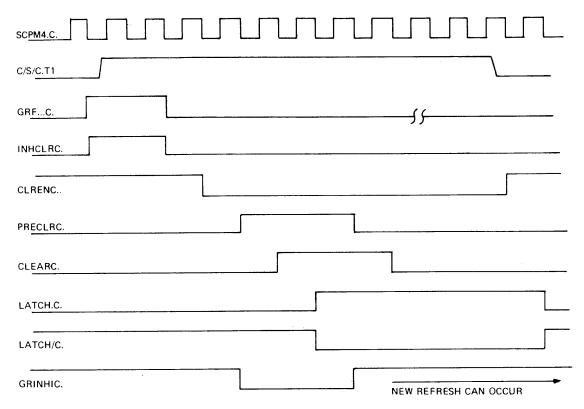

LR

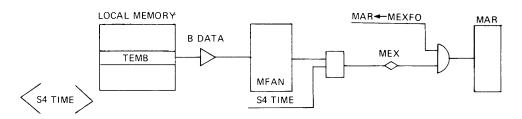

TEMPB (Temporary Buffer)

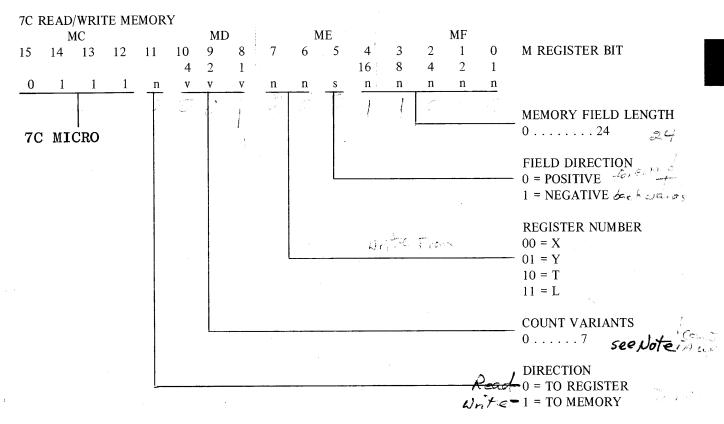

TEMPB is a temporary buffer in the right half of local memory. TEMPB is not addressable as a source or sink and is therefore not available to the programmer. The function of TEMPB is strictly hardware and its use is for the 7C Read/Write Memory micro or the 8D Scratchpad Relate FA micro. When used for either of these micros it is a temporary holding register. TEMPB is described in detail within Section II of this manual.

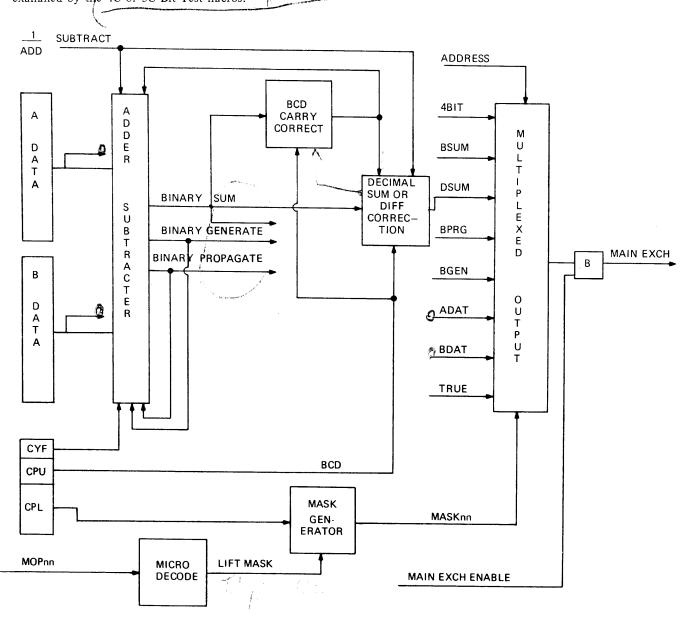

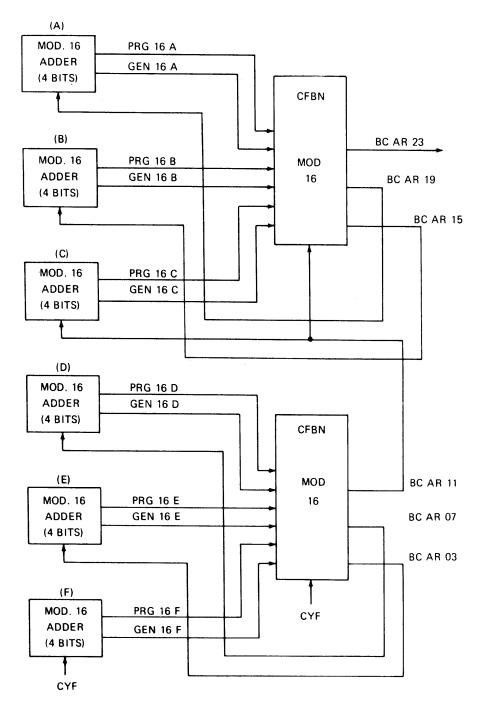

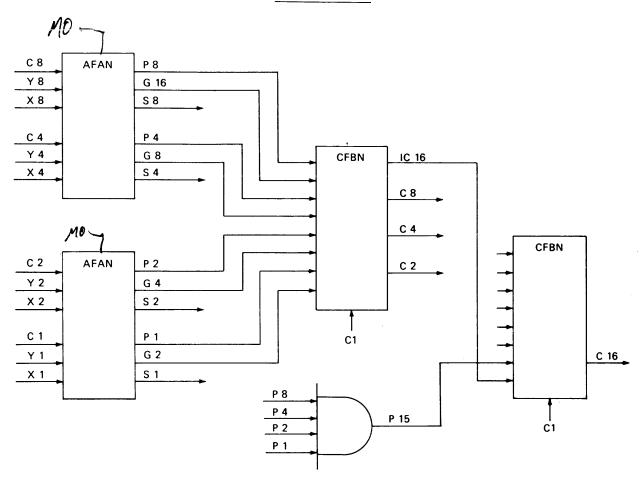

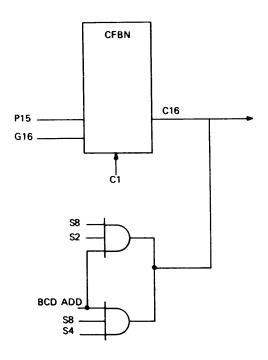

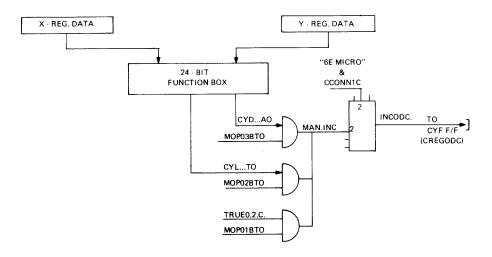

# 24 BIT ARITHMETIC AND COMBINATORIAL UNIT (24 BIT FUNCTION BOX)

The 24 Bit Function Box is used to produce the normal arithmetic or logic functions between two 24 bit operands.

# Input\_

Operand inputs to the function box are the X and Y registers and control inputs are CYF, CPU, and CPL which will be discussed as a portion of the C Register.

# Outputs.

Outputs of the Function Box include SUM, DIFFERENCE, AND, OR, EXCLUSIVE-OR, CARRY OUT, BORROW, EQUAL TO, GREATER THAN and LESS THAN functions. Also it has as outputs the complement of the X and Y Registers and the masked outputs of X and Y.

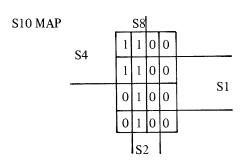

# Arithmetic

The arithmetic section of the function box is controlled by CPU, CPL, CYF and the operand inputs X and Y. The arithmetic operations consist of either an add or subtract with the operands being billiary data or four Bit BCD data designated by CPLL as follows:

CPU = 00 Binary 01 Four Bit BCD

10 UNDEFINED

11 UNDEFINED/

The operand length is defined by the value contained in CPL with a maximum value of 24 bits. If, for example, CPU = 01 and CPL = 24 then the operand input from X and Y is considered to be six 4-bit BCD characters. Either the SUM or DIFFERENCE is obtained by addressing the SUM or DIFFERENCE pseudo registers (SUM OR DIFF) via a Register Move type micro operator. In the case of the DIFFERENCE, the value in Y is subtracted from the value in X. The input CYF for a SUM is a carry in and for a DIFFERENCE is a borrow.

# Logic Functions - And/Or/Exclusive Or

The logical functions which may be obtained are addressed as pseudo source registers. The AND/OR/EXCLUSIVE OR functions are merely the ANDing, ORing or exclusive ORing of the contents of the X or Y. Those pseudo registers associated with these functions are XANY, XORY, and XEOY Registers. If the value in CPL is less than 24, then the most significant bits are filled with zeros.

#### One's Complement

The one's complement of the X and Y Register may be obtained by using a Register Move type micro which addresses either the pseudo CMPX or CMPY Register.

# Mask of X or Y

Normally by addressing the X or Y Register as a source, 24 bits are obtained. If less than 24 bits are desired the Mask of X or Mask of Y (MSKX or MSKY) pseudo registers may be addressed. Depending upon the value in CPL, from one to 24 bits ie. CPL=18 18 ... a which is 24 bits of X or Y may be obtained as source data with zero bits in the most significant bit positions.

# Conditions/States

In addition to the logical and arithmetic functions, the 24 Bit Function Box can produce various conditions/states which are addressable as source registers only. These conditions/states are referred to as the three pseudo registers-BICN (Binary Conditions), XYCN (X-Y Conditions) and XYST (X-Y States). All of the above pseudo registers are four bit registers and their functions with bits shown in Table I-1.

|     |               | and the same of th |            | _ |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|

| BIT | XYCN          | <b>BICN</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XYST       | 1 |

| ( 0 | $X \rangle Y$ | CYL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $X \neq 0$ | / |

| 1   | $X \land Y$   | CYD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $Y \neq 0$ |   |

| 2   | X = Y         | CYF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INT        |   |

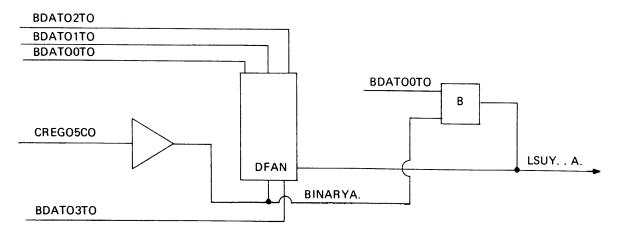

| 3   | MSBX          | LSUY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSUX       |   |

|     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /          |   |

|     |               | TABLE I-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1          |   |

|     |               | Condition St                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | atec       |   |

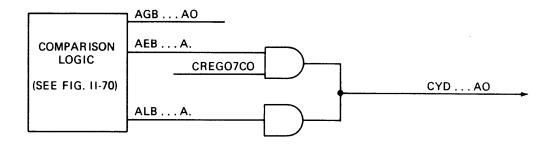

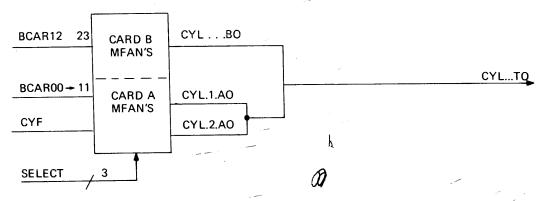

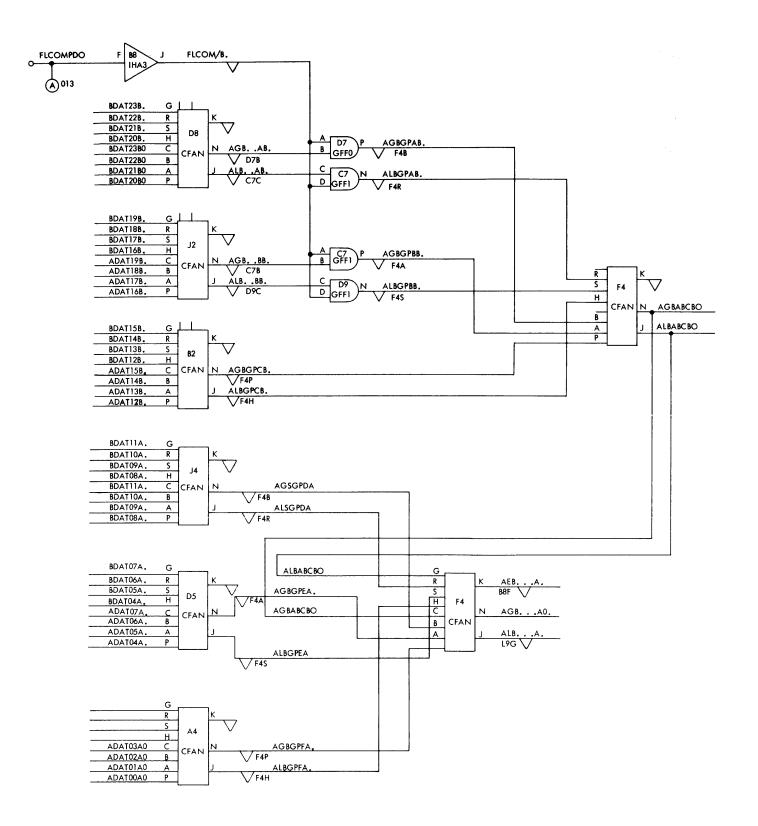

The XYCN Register produces the relational conditions of X is greater than, less than or equal to Y. The MSBX bit is true if the Most Significant Bit of the X Register as designated by CPL is true.

The BICN Register produces CYL which is a Carry Out Level, CYD a Borrow Out Level, status of CYF and LSUY. Least significant unit of Y (LSUY) is true if the least significant bit of Y is ONE and CPU = 00, or if CPU # 00 and the least significant four bits of Y is equal to nine (1001).

The four bit pseudo XYST Register checks and generates the  $X\neq 0$ ,  $Y\neq 0$ , INT or LSUX conditions. INT is an Interrupt and is true if one of the following interrupt is true:

Timer Interrupt

BUS I/O Interrupt

Console Interrupt

Memory Parity Error Interrupt

The LSUX (Least Significant Unit of X) bit is true if the least significant bit of X is ONE and CPU = 00, or if the least significant four bits of X equal nine (1001) and CPU  $\neq$  00.

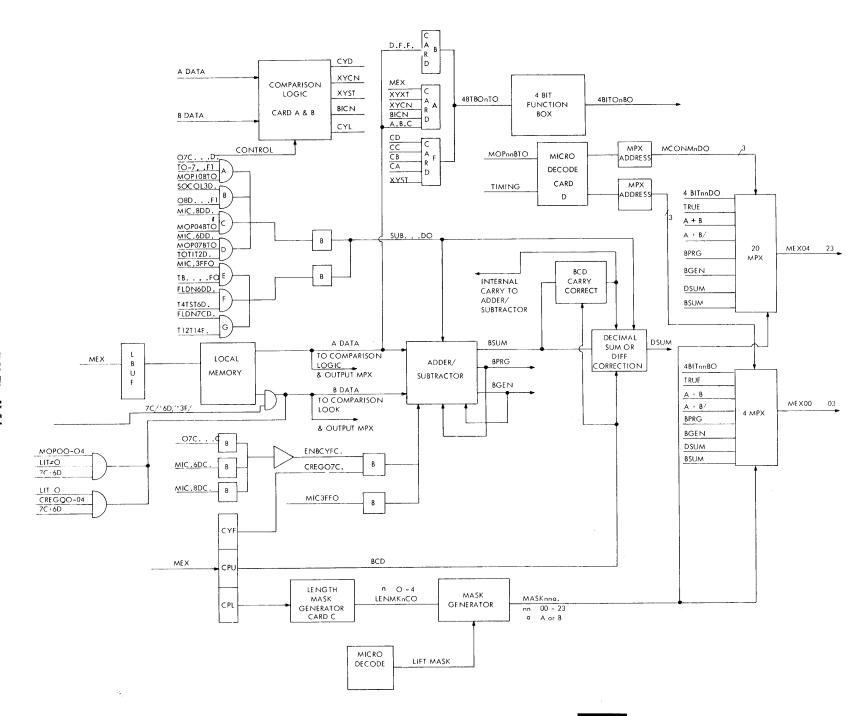

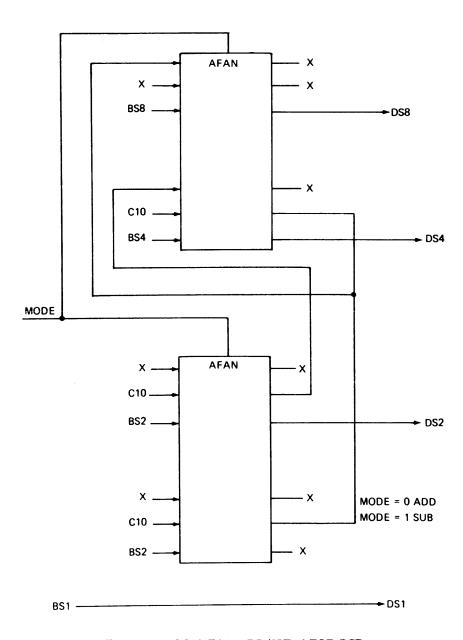

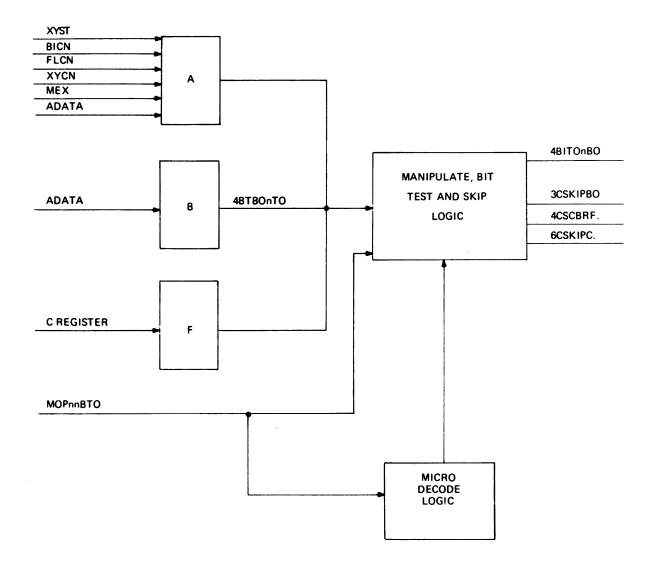

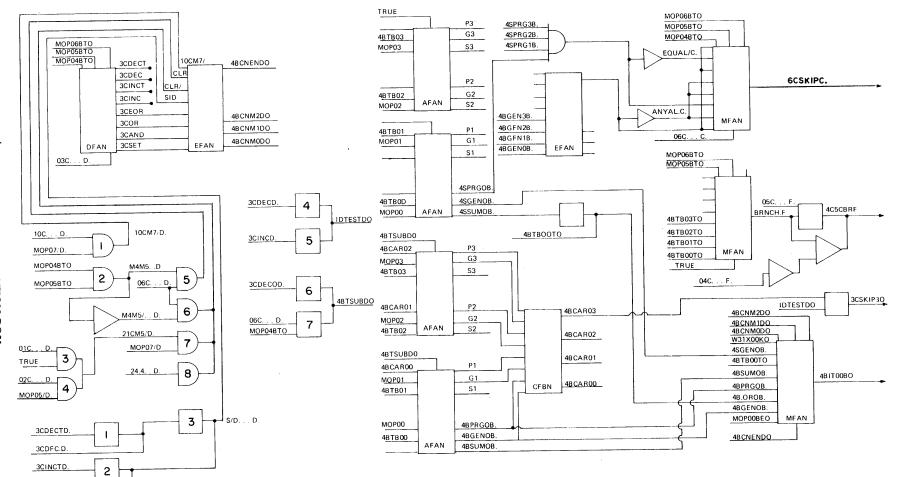

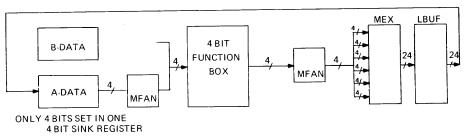

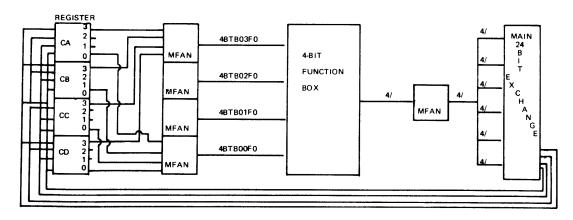

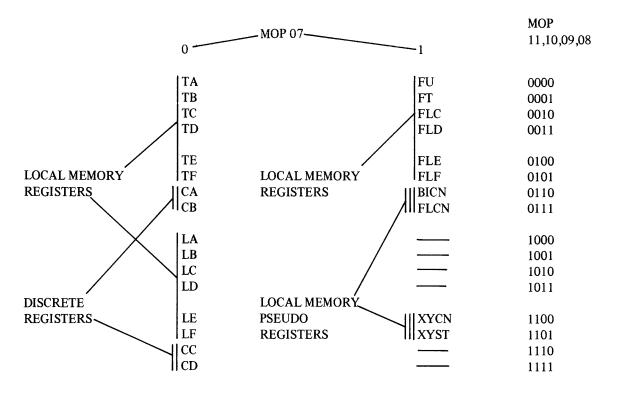

# FOUR BIT ARITHMETIC AND COMBINATORIAL SECTION (FOUR BIT FUNCTION BOX)

The Four Bit Arithmetic and Combinatorial Section otherwise referred to as the Four Bit Function Box is used to produce the normal arithmetic or logic functions between two 4-bit operands.

The Four Bit Function Box is also used to test various conditions of four bit registers and branch or skip on the results. The following is a description of the Four Bit Function Box.

### Inputs

Inputs to the Four Bit Function Box are any of the four bit registers that are listed in Table I-2 with a second input being obtained from the micro instruction itself.

# FOUR BIT FUNCTION BOX INPUTS

| TA   | TB   | TC   | TD  | TE  | TF  |

|------|------|------|-----|-----|-----|

| LA   | LB   | LC   | LD  | LE  | LF  |

| FU   | FT   | FLC  | FLD | FLE | FLF |

| CA   | CB   | CC   | CD  |     |     |

| BICN | XYCN | FLCN |     |     |     |

# Logic Functions

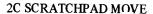

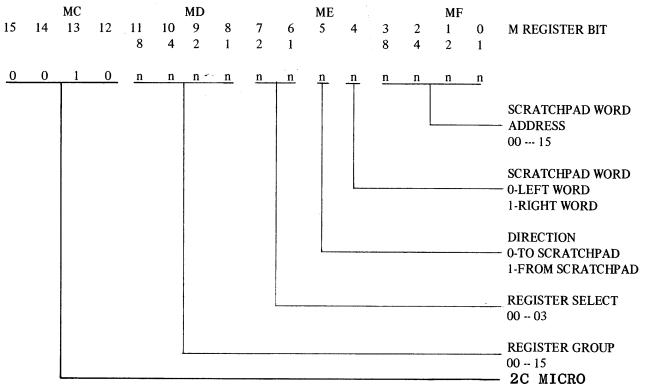

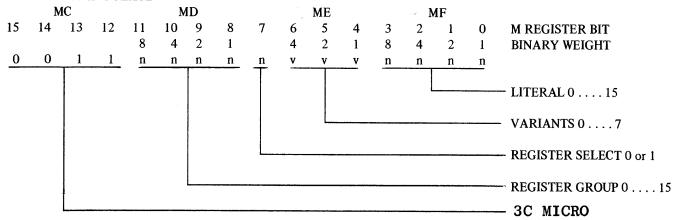

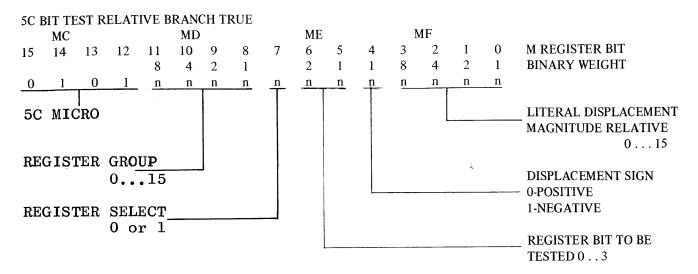

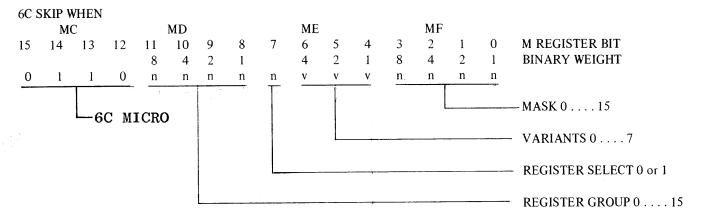

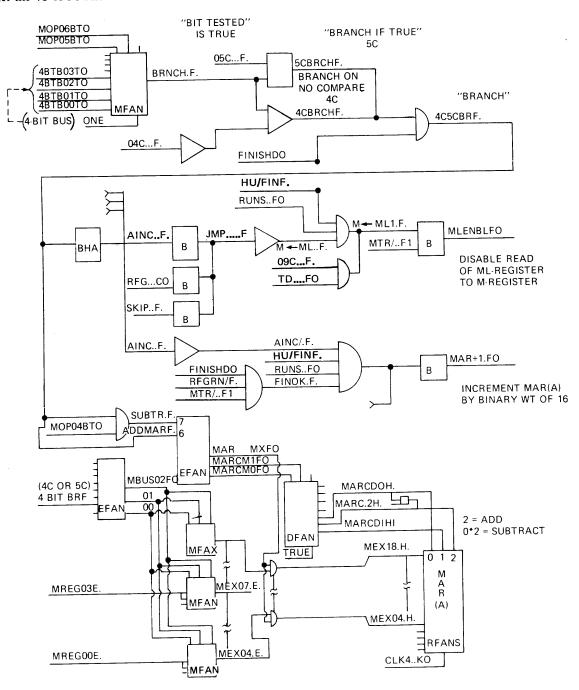

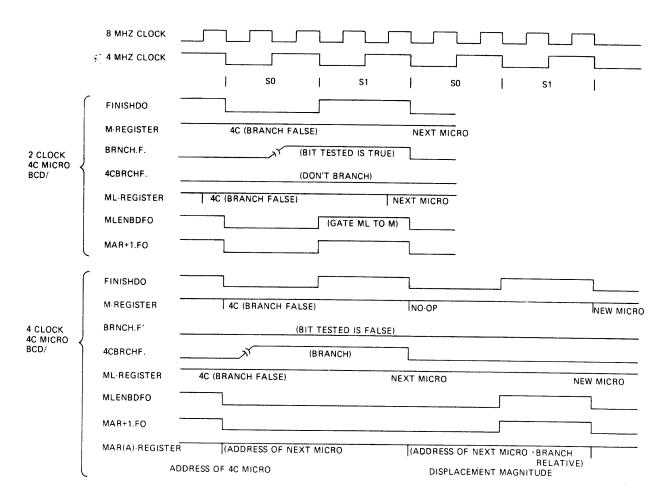

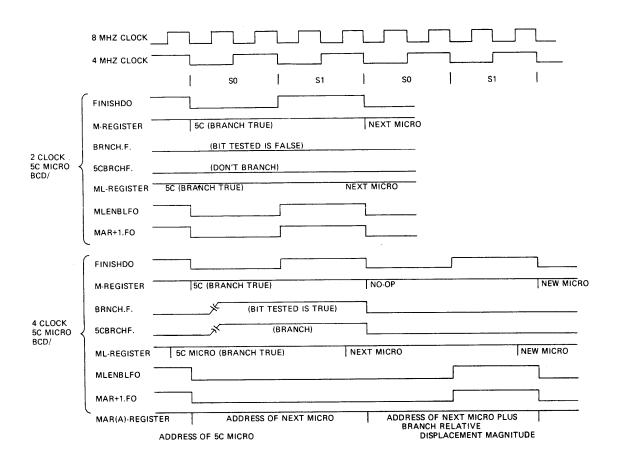

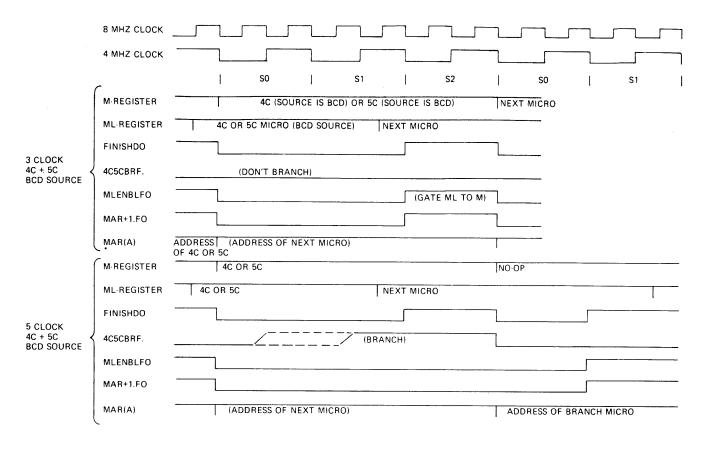

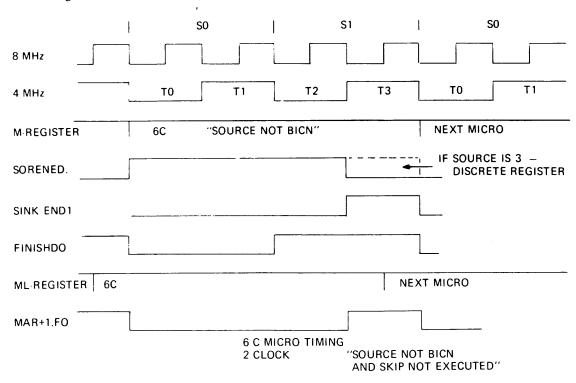

In addition to the development of the various logical/arithmetic functions such as SET, AND, OR, EXCLUSIVE-OR, BINARY SUM MODULO SIXTEEN and BINARY DIFFERENCE MODULO SIXTEEN, the Four Bit Function Box through specific micros can test one bit or combinations of bits in various four bit registers. The micros which perform some of the above functions are as follows: 1C Register Move, 2C Scratchpad Move, 3C Four Bit Manipulate, 4C Bit Test Relative Branch False, 5C Bit Test Relative Branch True and 6C Skip When. For a description of these micros as to function refer to the appropriate pages in Section I of this manual.

# REGISTERS

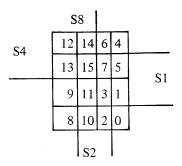

#### REGISTER SELECTION

The various registers of the B1700 system are addressed within the micro operator or from the front console by a series of coordinates.

The first coordinate is to select one of 16 groups of registers, the second coordinate then selects one of four registers from that group. Table I-3 illustrates the selecting of the register according to REGISTER GROUP and REGISTER SELECT. This chart must be used when generating or observing micro code in order to determine the designated register.

EXAMPLE: FB Register is register Group 9 and Register Select 2.

|            |    | REGISTER SE | ELECT  | The second |

|------------|----|-------------|--------|------------|

| REGISTER   | 0  | 1           | 2,     | 3          |

| GROUP<br>0 | TA | FU          | X      | SUM        |

| 1          | ТВ | FT          | Y      | CMPX       |

| 2          | TC | FLC         | Т      | СМРУ       |

| 3          | TD | FLD         | L      | XANY       |

| 4          | TE | FLE         | MAR(A) | XEOY       |

| 5.         | TF | FLF         | M      | MSKX       |

| 6          | CA | BICN        | BR     | MSKY       |

| 7          | СВ | FLCN        | LR     | XORY       |

| 8          | LA | RES.        | FA     | DIFF       |

| 9.         | LB | RES .       | FB     | MAXS       |

| 10         | LC | RES.        | FL     | MAXM       |

| 11         | LD | RES .       | TAS    | U          |

| 12         | LE | XYCN        | СР     | RES .      |

| 13         | LF | XYST        | RES .  | DATA       |

| 14         | CC | RES .       | READ   | CMND       |

| 15         | CD | CPU         | WRIT   | NULL       |

TABLE I-3 REGISTER TABLE

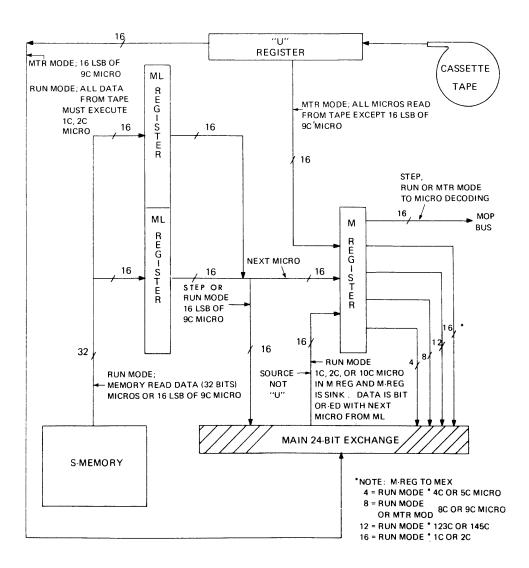

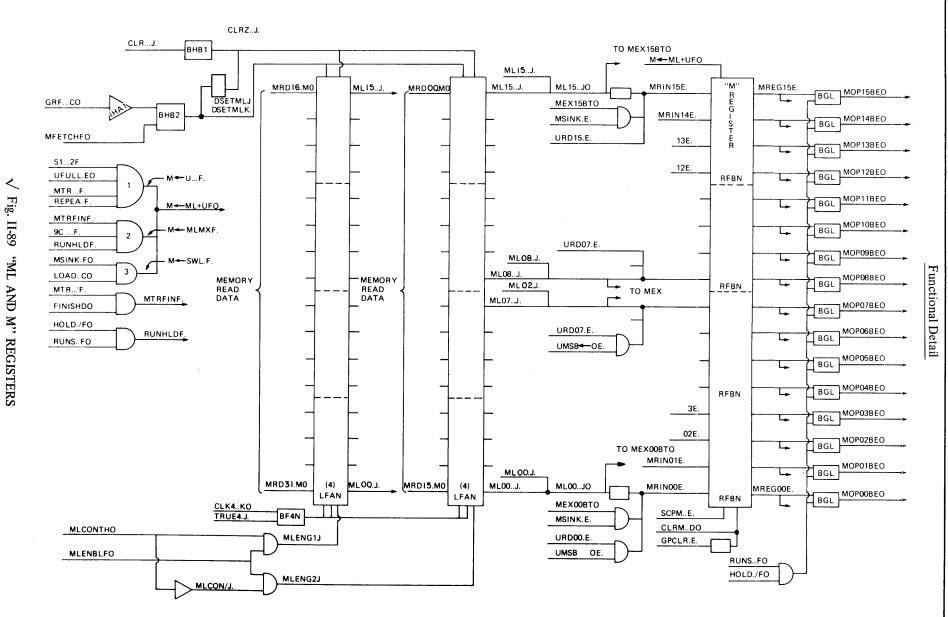

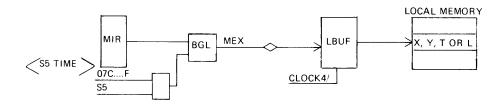

# M REGISTER (MICRO REGISTER) AND INPUTS

The M register is a 16 bit register (discrete) which is used to hold the active micro-operator that was previously obtained from S-Memory, or from the Tape Cassette in Tape Mode. The contents of this register is decoded in various areas of the processor to enablethe micro to perform its designated function. The M register is addressable both as a source, and as a sink. When it is used as a sink, the incoming data is bit ORed with the next incoming micro, thus modifying the new micro being placed in M for execution.

The M register has two sources from which it can receive micros:

- A. S-Memory via Memory latches (ML)

- B. U Register (to facilitate micro execution in Tape Mode)

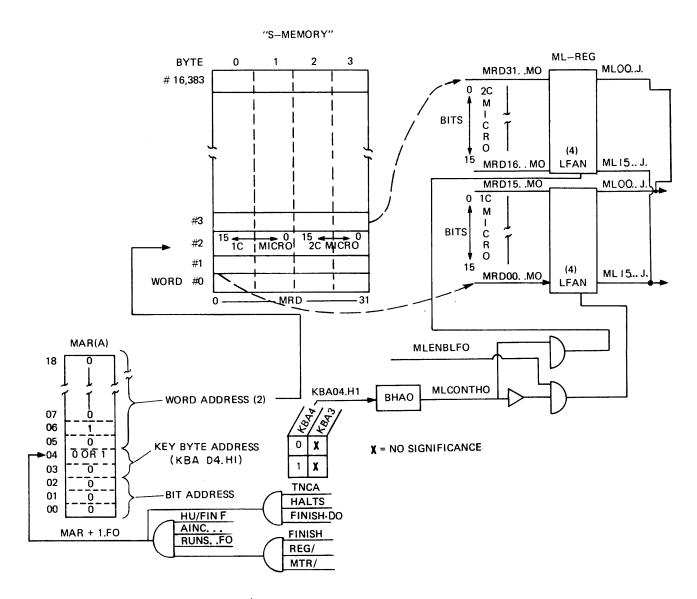

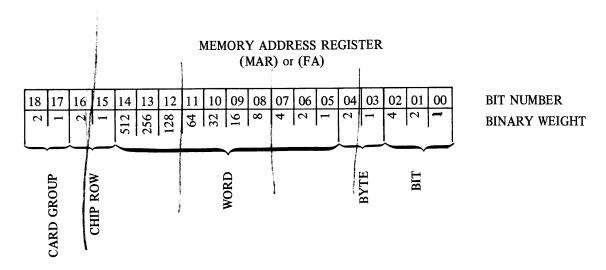

# MAR (A) REGISTER (MEMORY ADDRESS/ADDRESS REGISTER)

The MAR (A) Register is a 19 bit micro-program address register. The MAR (A) Register has two basic functions and in actuality is a shared register for addressing memory at two specific times. As a program address register it is referred to as the A Register, and addresses 16 bit micro operators in main memory by assuming them to be located at bit boundary addresses exactly divisable by 16. When used in this manner the lower order four bits are ignored and the micro is fetched and stored in the M Register. In the case of the micro fetch ("M" FETCH), the memory rotator is by-passed.

The MAR (A) Register is capable of having binary increments from 0 through 4095 (multiplied by 16) added to or subtracted from it with a high speed adder to facilitate program branching. The MAR (A) Register is automatically incremented by binary 16 during the run mode. Wrap-around of MAR (A) can occur and is permitted.

The MAR (A) Register also serves as a Memory Address Register (thus the name MAR) for the Read/Write Memory micro operator. In this case the full 19 bits of MAR (A) are used and the address is a bit address. The data read/written is passed through the rotator to insure the data is placed in the proper memory locations due to variable field length, variable field direction and the bit addressability of the memory. When used as a Memory Address Register, the address of the next micro (A Register function) is temporarily stored in a holding register, referred to as Temporary Buffer (TEMPB).

The MAR (A) Register is addressable as a source and as a sink. When addressed as a source, all bits are produced onto the Main Exchange. When used as a sink, the rightmost four bits of the source are moved to the rightmost four bits of the MAR (A) Register although they are not significant. Moves into the MAR (A) Register cause the instruction address to change and are therefore regarded as branches.

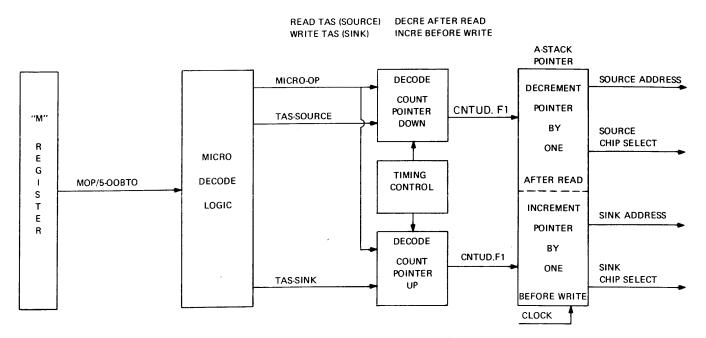

### TAS REGISTER (TOP OF A STACK REGISTER)

The TAS Register is a 24 bit register which is the top of the A Stack. The top of the A Stack is addressed by a stack pointer that can be changed by moves into the A Stack or by moves from the A Stack. Because the pointer addresses different A Stack locations, the TOP of the A Stack is a relative position within the A Stack. Moves into TAS cause the A Stack Pointer to first be upcounted, and then, the source data is stored in the location addressed by the pointer. Moves from TAS cause the data in the A Stack location which is addressed by the Stack Pointer to be read and placed in the destination register. After the read occurs the Stack Pointer is decremented and a new A Stack location is addressed which becomes the new TAS.

# A STACK

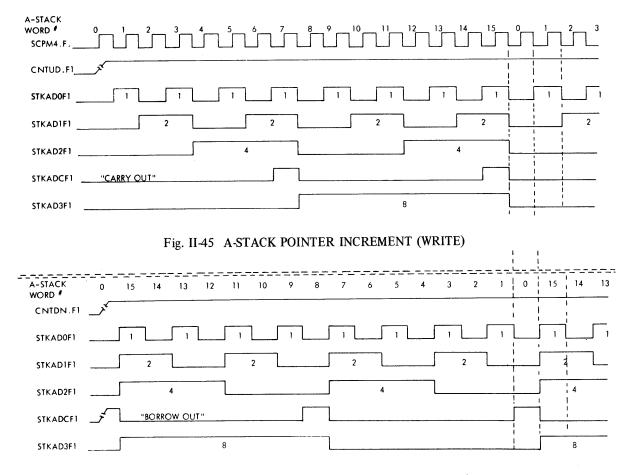

The A Stack is a 16 words deep, 24 bit wide memory. Generally the A Stack is used for normal Call/Return programming where subroutines may be obtained and upon completion of the subroutine, control is returned to the program. The Call/Return is obtained by CALLING a subroutine (branching) and storing the address where the program exited in the A Stack. Return from the subroutine is then done by moving the contents of the A Stack to MAR(A) which acts as a BRANCH back into the normal program.

The A Stack operates as a push down stack with a last in, first out structure. The A Stack is addressed by a Stack Pointer and wrap around of the pointer is provided. Sixteen consecutive writes (pushes) into the A Stack or sixteen consecutive reads (pop) from the A Stack will cause the pointer to address the same location as it did at the beginning of the write or read operations. Although the A Stack is not intended to be used as an operand stack (data storage), it has been purposely made 24 bits wide to allow for limited operand storage. (Scratchpad usually provides for data storage.)

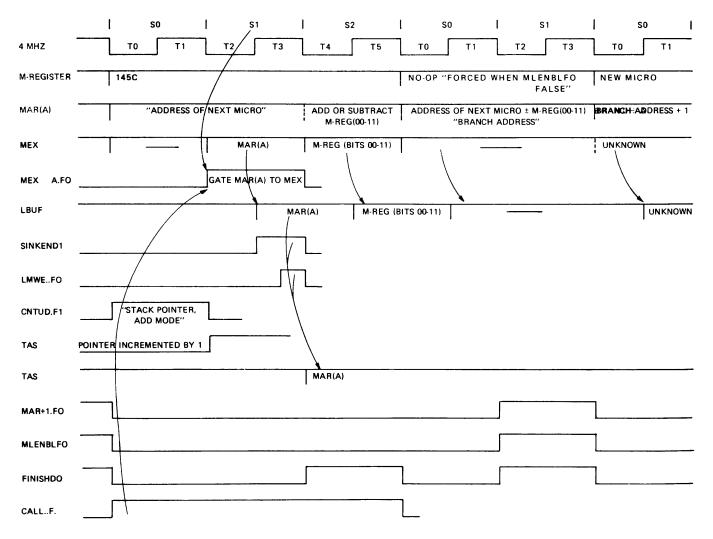

The only micro which has a specific affect on the A Stack other than the Register Move type micros is the 145C Call.

Refer to the 145C Call micro for the specific function of the A Stack with this micro.

# MAXS REGISTER (MAXIMUM S-MEMORY REGISTER)

The MAXS Register is a 24 bit register which is set by the field engineer to indicate the maximum size of the installed memory. The MAXS Register is not a discreet register but is wired constant and thus addressable as a source register only.

# BR AND LR REGISTER (BASE AND LIMIT REGISTER)

The Base and Limit Registers are both 24 bit registers which can be addressed as either a source or destination. These registers are used for protection of memory and base relative addressing. Memory Addressing within the Base and Limit registers is generally allowed. If the address does not fall within the Base and Limit then it is a software function to determine whether the cycle is to be allowed.

# MAXM REGISTER (MAXIMUM M-MEMORY REGISTER)

M-Memory is not available as an option in the S-Memory Processor and by addressing this register as a source all zeros will be obtained. All zeros indicates that M-String is not present.

#### X REGISTER

The X Register is a 24 bit general purpose register and used primarily for the storage of an operand for the 24 Bit Function Box. The register may be addressed as either a source or destination. In addition to its input to the 24 Bit Function Box, it is one of four registers (X, Y, T and L) which may be used as a source or destination for data on a memory operation. The X Register is also capable of being shifted or rotated by the 4D, 5D or 3F micro operators.

On an add operation the X Register will contain the addend and on a subtract operation the X Register contains the minuend.

#### Y REGISTER

The Y Register is a 24 bit general purpose register and used primarily for storage of an operand for input to the 24 Bit Function Box. (See X Register) The Y Register may be addressed as either a source or destination. In addition to its input to the 24 Bit Fuction Box it is one of four registers (X, Y, T, and L) which may be used as a source or destination for data on a memory operation. The Y Register is also capable of being shifted or rotated by the 4D or 5D micros. On an add operation the Y Register will contain the augend and on a subtract, it contains the subtrahend.

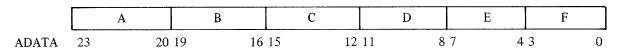

# L REGISTER (LOGICAL REGISTER)

The L Register is a 24 Bit general purpose register and is also addressable in four bit groups denoted as LA, LB, LC, LD, LE, and LF. The L Register may be used as a 24 bit source or destination or can be addressed in the above mentioned four bit groups as a source or destination. Since the L Register is addressable in four bit groups, its contents are available for analysis and alteration via the four Bit Function Box. The L Register is one of the four registers (X, Y, L, and T) which may be used as a source or destination for data on a memory operation.

# T REGISTER (TRANSFORM REGISTER)

The T Register is a 24 bit general purpose register used as either a source or destination. The T Register is addressable in four bit groups denoted TA, TB, TC, TD, TE, and TF. Since the T Register is addressable in four bit groups, it is available for analysis and alteration via the Four Bit Function Box.

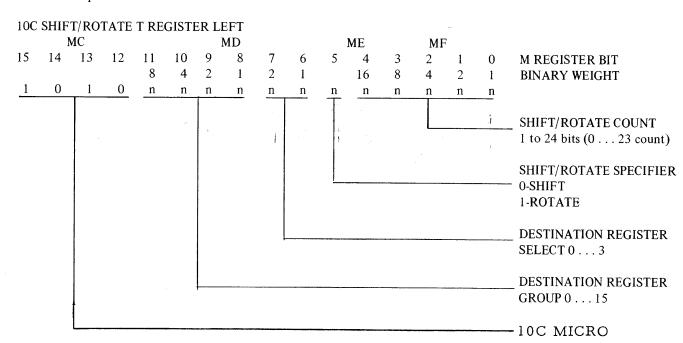

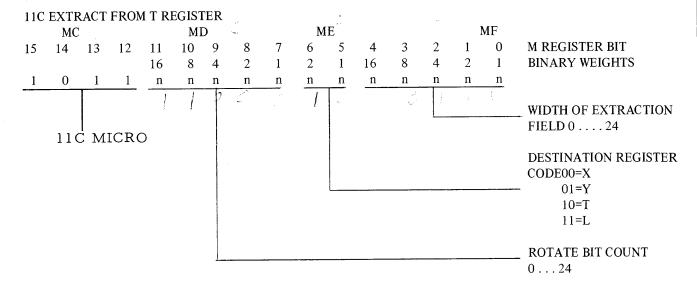

The T Register is one of the four registers (X, Y, L and T) which may be used as a source or destination for data on memory operations. The T Register is capable of Shift/Rotate operations (10C micro), and data may be extracted from the T Register (11C micro).

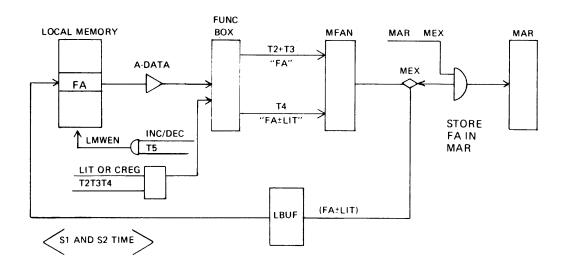

#### FA REGISTER (FIELD ADDRESS REGISTER)

The FA Register is a 24 bit register used to hold an absolute bit address for Main Memory. It has the capability of directly addressing any bit in the memory starting at any location. The FA Register is addressable as both a source and destination and can be loaded, stored or swapped with the contents of a word in the Scratchpad. FA is upcounted or downcounted by a literal value in the 7C Read/Write memory micro or by the value in CPL if that literal is equal to zero. A separate micro 6D Count FA/FL may be used to count FA up or down depending upon the variants of the micro.

On memory operations the FA Register is transferred to MAR(A) which will be used to address the memory location. In this case the upper five bits of FA are truncated but this is not significant as FA has the capability of addressing more memory than will be available in the machine.

#### **FB REGISTER**

The FB Register is a 24 bit register which can be functionally divided into three portions; a Four Bit FU (Field Unit) Register, a Four Bit FT (Field Type) Register, and a 16 Bit FL (Field Length) Register.

NOTE: Field Type is not specifically defined by the hardware and therefore has only specific meaning to the software.

The FB Register as well as each four bit portion of FB, denoted as FU, FT, FLC, FLD, FLE and FLF is addressable as a source and destination. In addition, the 16 bit portion denoted as FL is addressable as a source and destination.

The FU Register holds the length of the unit which makes up a field of data in memory such as binary and four bit BCD. FL holds the total length of the field with FL having the capability of describing fields up to 65,536 bits. FL may be adjusted up or down by a literal in the 7C Read/Write Memory micro, by the value in CPL or specifically by a 6D Count FA/FL micro.

FB has the ability of being loaded, stored or swapped along with FA into a Scratchpad memory word. FU and FL along with corresponding portions of the first cell or Right Scratchpad are used to set the various conditions of FLCN (Field Length Conditions) and the various conditions of the CP Register (See Bias micro 3E.)

#### SCRATCHPAD MEMORY

Scratchpad Memory consists of sixteen 48 bit words (16 x 48), or could be regarded as consisting of thirty-two 24 bit words (32 x 24). Scratchpad from a hardware standpoint is regarded as general purpose storage but its typical use is for storage of S-Language (See software concept) stack pointers or processor registers which are under constant manipulation.

The first cell of right scratchpad is referred to as SFL and SFU, which correspond to FL and FU in the FB portion of the F Register. SFL is used for comparison to FL for the FLCN (Field Length Conditions) and SFU is used if selected by the appropriate variants in conjunction with the 3E Bias micro.

# C REGISTER (CONTROL REGISTER)

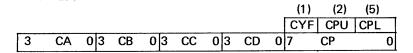

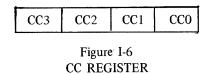

The C Register is a 24 bit register which is NOT addressable as such. The C Register may be addressed by four bit groups referred to as CA, CB, CC and CD. The least significant eight bits may be addressed as CP. CP may further be divided into three sections: CPL equal to five bits, CPU equal to two bits and CYF being one bit. Figure 1-5 illustrates the addressing portions of the C Register.

Fig. I-5 C REGISTER

The CA and CB portions of the C Register do not have any specific hardware use and are, therefore, described as general purpose four bit storage registers.

The CC portion is used for storage of various processor interrupt conditions or the processor state. The bits of CC are defined as follows:

- CC(0) Console Interrupt derived from the console interrupt button.

- CC(1) Bus Interrupt derived from the various I/O Controls attached to the B1700 I/O Bus. This bit is set as a result of a service request by one or more of the controls which may be attached to the I/O Bus.

- CC(2) Timer Interrupt is developed from the primary power frequency. The Interrupt occurs every 100 milliseconds to set CC(2).

NOTE: Adjustable by the Field Engineer for either 50 Hz or 60 Hz.

CC(3) Console State Lamp. The setting of CC(3) by software causes the Console State Lamp to illuminate. Use of the State Lamp is defined by software.

The CD portion of the C Register is also used for storage of interrupt conditions. CD(3) will be set if a parity error occurred on a memory read operation that was initiated by the processor. CD(2) thru CD(0) is reserved.

The CPL portion (Control Parallelism Length) is used to define the data length of the 24 Bit Function Box or used to define length at various times, such as if the literal in the 7C Read/Write Memory micro is equal to zero, then the value in CPL is used. CPL is a five bit register and defines lengths of one to twenty-four bits.

CPU is the Control Parallelism Unit of the CP portion of the C Register. The CPU Register is two bits and defines the unit of data as either binary or Four Bit BCD.

CPU=00 Binary Data

CPU=01 Four Bit BCD Data

CPU=10 Reserved

CPU=11 Reserved

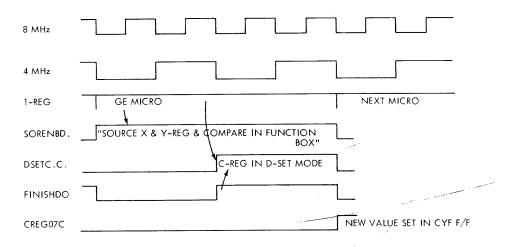

CYF is the Carry Flip-Flop and used to store overflows from the 24 Bit Function Box as a result of an add or subtract operation but must be set by sampling the appropriate level from the function box. (See 6E micro, Carry Flip-Flop Manipulate.)

All four bit portions of the C Register are addressable as both a source and destination. Their contents are available for analysis and alteration via the Four Bit Function Box.

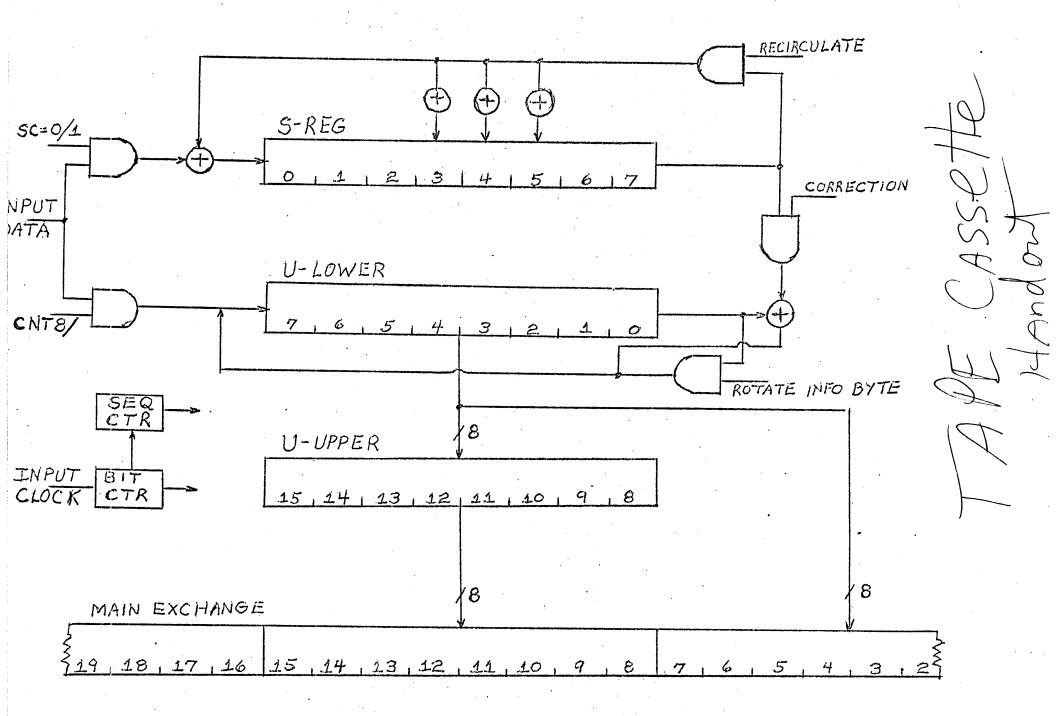

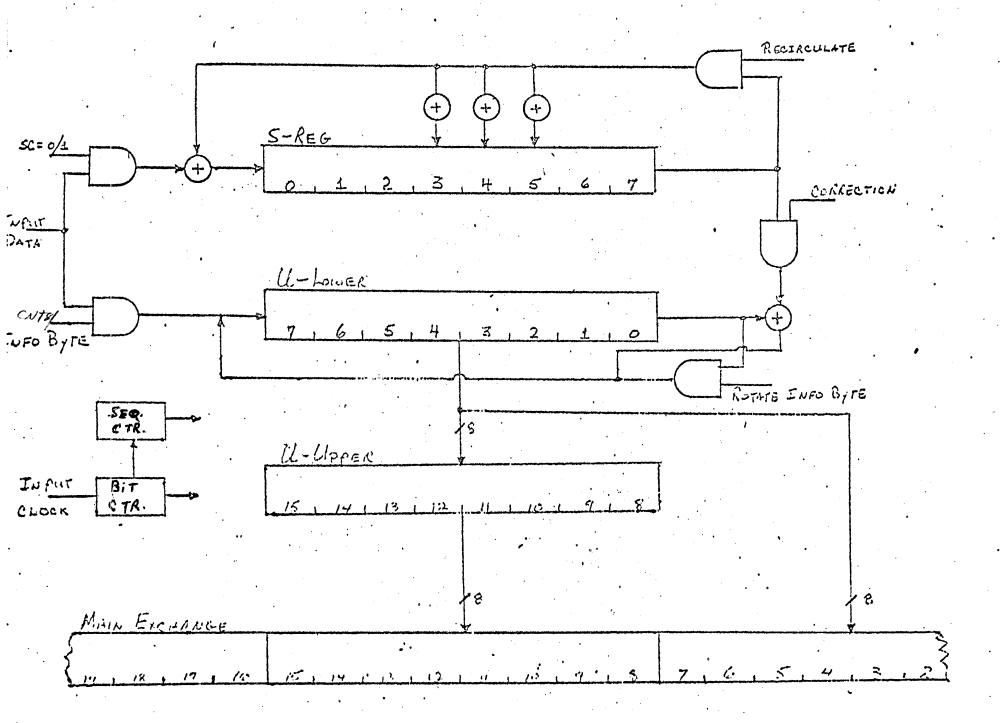

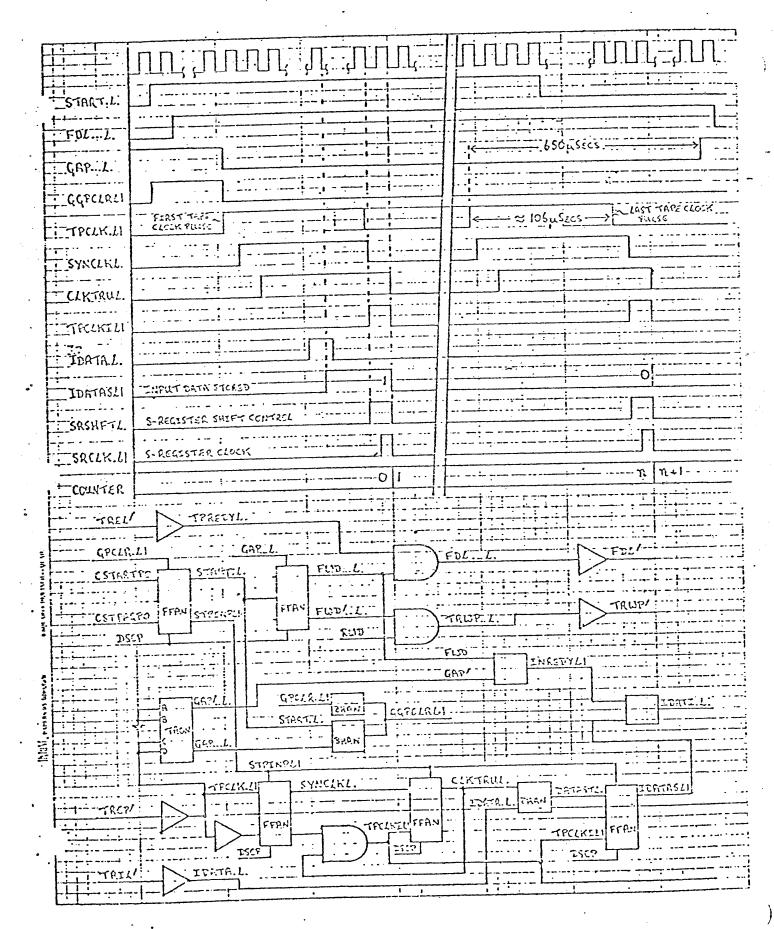

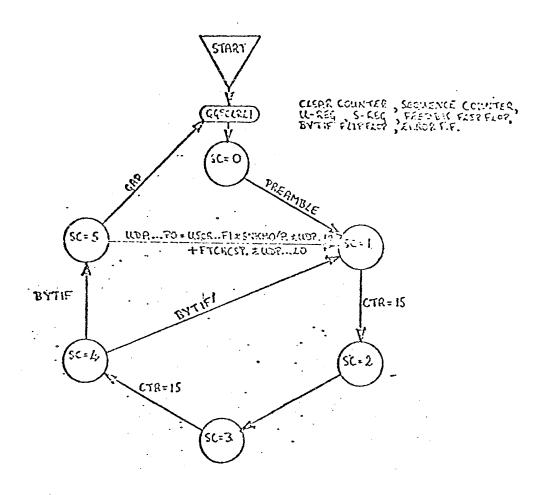

# U REGISTER

The U Register is a 16 bit register used primarily to accumulate the bit serial input from the console cassette tape loader. The U Register is addressable only as a 16 bit source and NOT a destination. Only the micro 1C Register move can access the U Register. If the data is not yet available in the register, the micro 1C finish is delayed until the U Register is full.

In the Tape Mode the contents of the U Register are directly transferred to the M Register in order to cause the execution of micros from the tape. If the micro Read is a 9C move 24 bit literal then Execution is delayed until the remaining 16 bits of the literal have been accumulated in the U Register.

## FLCN REGISTER (FIELD LENGTH CONDITIONS)

The FLCN Register is a four bit pseudo register which indicates comparison conditions. FLCN is a static comparison between the FL portion of the FB Register and the corresponding portion of the first word of right scratchpad referred to as SFL. FLCN carries the conditions listed in Table I-4.

| BIT | CONDITION     |

|-----|---------------|

| 0   | FL <b>#</b> 0 |

| 1   | FL < SFL      |

| 2   | FL > SFL      |

| 3   | FL = SFL      |

TABLE I-4

FIELD LENGTH CONDITIONS

# CMND REGISTER (COMMAND REGISTER)

The CMND Register is a 24 bit pseudo register which can act only as a destination. A Register Move type of operation with CMND as the destination will cause a command to be transferred on the I/O BUS and the Command Active signal (CA) is generated. This operation is used to transfer a Command to an I/O Control on the I/O Bus.

# **DATA REGISTER**

The Data Register like the Command Register is a 24 bit pseudo register but it can act as both a source and destination. The Data Register is used to transfer data to and from the I/O Controls attached to the I/O Bus. When used as a source, the processor generates the Response Complete (RC) signal and accepts the 24 bits of data from the I/O Bus. When used as a destination, the processor generates the RC signal to the I/O interface and places the data from a source register on the I/O bus.

# **NULL REGISTER**

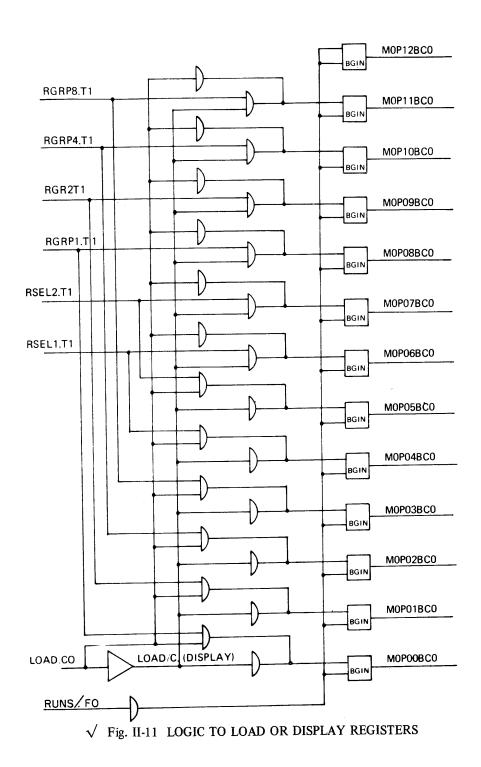

NULL is a pseudo register with a length of 24 bits. NULL is used primarily on a load or display of a designated register from the Front Panel (Console). In the Halt Mode the hardware will generate moves from NULL in order to cause the contents of the console switches to be loaded in the designated destination register. This is accomplished by depressing the LOAD button on the Console. If the Load Button is not depressed the hardware in the Halt Mode generates a Register

move to NULL which will cause the designated register to be displayed on the console lamps.

In the Run Mode or Tape Mode, the NULL Register may be moved to a register for the purpose of clearing that register. (NULL is equal to all zeros.)

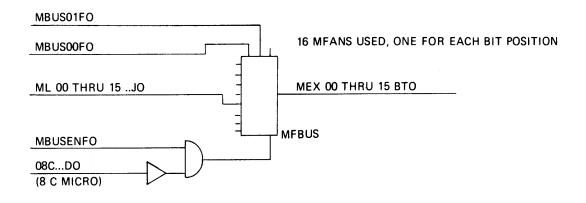

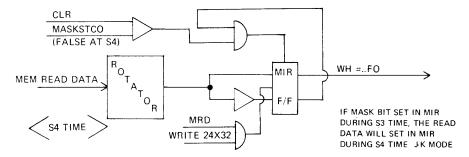

# MEMORY REGISTER AND ASSOCIATED LOGIC

The registers associated directly with memory such as MIR (Memory Information Register) and MLR (Memory Latch Register) along with associated memory logic such as the rotator are generally described in the S-Memory portion of Section I of this manual (refer to index).

# MICRO OPERATORS

#### INTRODUCTION

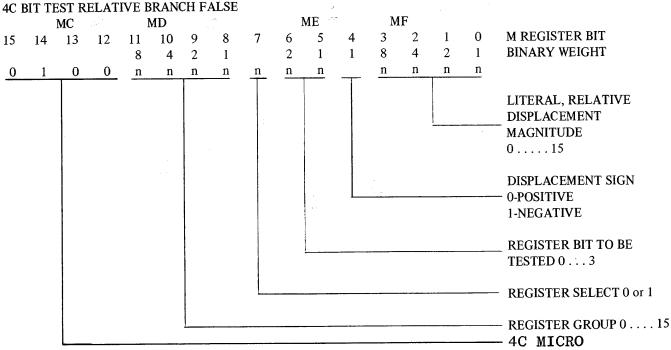

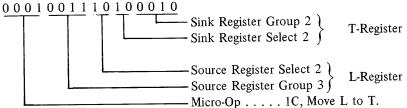

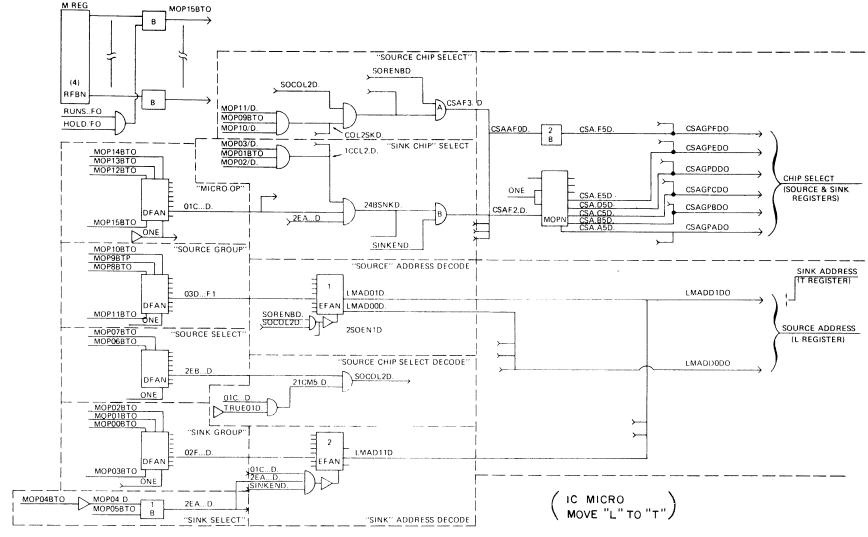

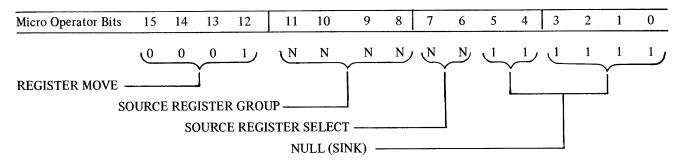

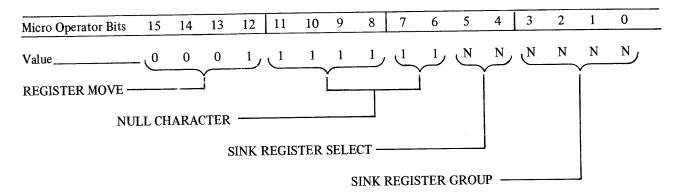

The B1700 Micro Processor has the capability of producing approximately 60 different micro instructions. It was necessary to develop only 24 of the possible 60 combinations and Table I-5 lists those 24 micros which have been implemented. The micros are referred to by name and by binary weight within the specific portion of the M Register. The 1C Register Move for example has a binary weight of 1 in the MC Register. The other bits of the 1C Register Move are used for selection of source and sink registers according to Table I-3. The variants for various micros are listed in Table I-5 but for a more detailed explanation of the micro and variants refer to the individual micro operator descriptions.

# 1C REGISTER MOVE

Move the contents of the source register to the destination register. If the move is between registers of unequal lengths, the data is right justified with left (most significant) zero bits supplied or with data truncated from the left whichever is appropriate.

The contents of the source register are unchanged unless it is also the destination register.

The basic execute time is two clocks to which is added one additional clock if the source is BCD, and two additional clocks if the destination is the MAR (A) register. If the U-Register is the source, the time takes many clocks.

# Exceptions:

- 1. CPU and CMND are excluded as source registers.

- 2. When M is used as a destination register, the operation is changed to a bit OR which modifies the next micro-operation. It does not modify the instruction as stored in the memory.

- 3. BICN, FLCN, XYCN and XYST are excluded as destination registers.

- 4. All registers and pseudo registers in column select=3 are excluded as destination registers except CMND and DATA.

- 5. When DATA is designated as a source, CMND and DATA are prohibited as destinations.

- 6. U is excluded as a source register in STEP and TAPE mode. It is permitted as source in RUN mode. However, when U is used as a source the TAS, A and M registers are excluded as destination registers.

TABLE I-5

| 7       | ALL<br>CLR         | ANY/<br>CLR/ | ALL /<br>CLR / | EQL /<br>CLR / | ALL /<br>CLR | 6 LA RES FA DIFF<br>9 L6 FB MAXS<br>10 LC FL MAXM<br>11 LD TAS U                                                                                                                                                                                                                                                                                                  | æ                                                 |

|---------|--------------------|--------------|----------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|         | ΓΑ •<br>F L •      | FA t         | FA +           | F 1            | FA P         | II LD TAS U  12 LE XYCN CP RES 13 LF XYST RES DATA 14 CC RES READ CHIND 15 CD CPU WRIT NULL                                                                                                                                                                                                                                                                       | urrough                                           |

| 5.      | ROT → RES. FA! FL+ | FA+<br>FL+   | FA+            | FL+            | FA + FL +    | INDIVIDUAL BITS OF SOME 4-BIT REGISTERS HAVE SPECIAL MEANINGS AS NOTED BELOW: NOTE: BITS ARE NUMBERED HERE ACCORDING TO THE HARDWARE CONVENTION:  LALBIC LDILE LF 3 0,3 0,3 0,3 0,3 0,3 0 MSB L LSB 123 BIT # BICN XYCN XYST FLCN 0 CYL X>Y X 10 FL 10 1 CYD X>Y 10 FL 10 2 CYF XY INTO FL 25FL 3 LSDY MSBX LDDX FL 25FL INT OR ANY 1 OR MORE OF: CCO CCI CC2 CD3 | Burroughs - B1700 Central System Technical Manual |

| 0N<br>Y | FS                 | UNDEF<br>NØP | FCP            | UNDEF<br>NØP   | UNDEF        | CC & CD  CCO CONSOLE SOFT HALT INTERRUPT.  CCI I/O BUS SERVICE REQUEST INTERPT.  CC2 REAL TIME CLOCK (00 Mg) INTERPT.  CC3 STATE FLANT EMPS (A FED COL) CONSOLE)  CD1 RESERVED  CD2 RESERVED  CD2 RESERVED  CD3 MEMORY READ DATA PARITY EAROR INTERRUPT                                                                                                           | anual                                             |

|         |                    |              |                |                |              |                                                                                                                                                                                                                                                                                                                                                                   | Sec. I Page 13                                    |

|            | MICRO NAME                   | 15  | M(    |          | 12          | ļ ,          | M (   | 9 ,           | 8    | 7             | 6 ME         | 5           | 4          | 3        | 2<br>L       | IF<br>       | 0     | VARIANT    | s d      | 000         | 001            | 010              | 011          | 100          | (0)         | 110          | . 111          | ,                                                                                                            |              |

|------------|------------------------------|-----|-------|----------|-------------|--------------|-------|---------------|------|---------------|--------------|-------------|------------|----------|--------------|--------------|-------|------------|----------|-------------|----------------|------------------|--------------|--------------|-------------|--------------|----------------|--------------------------------------------------------------------------------------------------------------|--------------|

| 10         | REGISTER MOVE                | ٥   | 0     | 0        | 1           | REG          | 1 GR  | OUP<br>GISTE  |      | REG           |              | REG<br>SELE |            |          |              | GROU         |       |            |          |             |                |                  |              |              |             |              |                | REGISTER SELECT                                                                                              | -            |

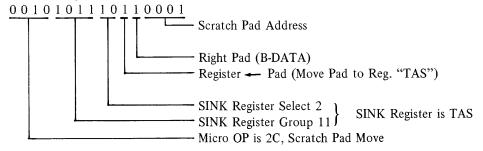

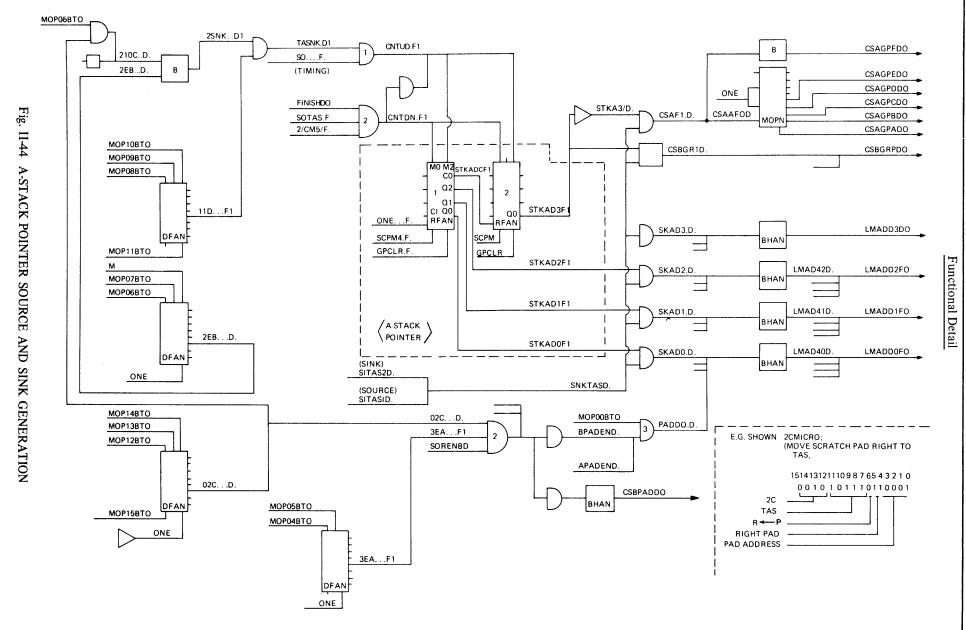

| 2 C        | SCRATCHPAD MOVE              | ٥   | 0     | ı        | 0           | REGIS        | STER  | GROU          | P    | RE            | G A          | AOV C       |            | DOUB     |              | AD WO        | ORD   | MOV DIR    |          |             | R ← P<br>RIGHT |                  |              |              |             |              |                | REGISTER 0 1 2 3                                                                                             |              |

| 3 C        | 4 BIT                        | 0   | 0     | 1        | 1           | REGIS        | TER   | GROUP         | >,   | REG           | MANI         |             | TE         |          | T MA         | NIP          |       | MANIP      |          | SET         | AND            | OR               | EOR          | INC          | INC<br>TEST | DEC          | D E.C<br>TE ST | I THE FT Y CMPX 2 TC FLC T CMPY 3 TD FLD L XANY                                                              | - 1          |

| 4 C        | BIT TEST REL                 | 0   | 1     | 0        | 0           | REG          | STER  | GROU          | iP   | REG<br>SEL I  | TEST         | BIT         | DSP        | REL      | LATIV        | E BRA        | MAG   | DSP SIGN   |          | -           | _              |                  |              |              |             |              |                | 4 TE FLE MAR(A) XEOY                                                                                         | ı            |

|            | BRANCH FALSE<br>BIT TEST REL | 0   |       | 0        | 1           | REGI         | STER  | GRO           |      | REG '         | TEST         | SIT I       | D5P        | RELA     | ATIVE        | E BRA        | NCH   | DSP SIGN   | 1: 4     | +           | -              |                  |              |              |             |              |                | 5 TF FLF M M5KX<br>6 CA BICN BR M5KY<br>7 CB FLCN LR XORY                                                    |              |

| 5C         | BRANCH TRUE                  | 0   |       | <u>1</u> | 0           | REGI         | STER  | GROU          |      | REG           | SKIP         | TE5         | т          |          |              | ST M         |       | SKIP TE    |          | ANY<br>CLR/ | ALL<br>CLR/    | EQL<br>CLR/      | ALL          | ANY/         | ALL /       | EQL /        | ALL /          | 6 LA RES FA DIFF                                                                                             | ١,           |

| 6 C        | READ/WRITE                   | 0   |       | <u> </u> |             | R/W          | COUN  | T FA          | FL.  | DATA          | REG          |             | Ċ          |          |              | ANSF         |       | R/W VAR    | F        | READ        | WRT            | CLK/             | FAT          | FA           | FA+         |              | FAI            | IO LC FL MAXM II LD TAS U  IZ LE XYCN CP RES.                                                                | Ĭ            |

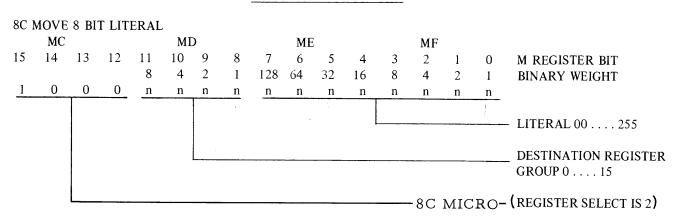

| 7C         | MEMORY<br>MOVE B BIT         | -   | 0     | 0        | 0           |              |       | GROU          |      | ENTI          | RE B         |             |            |          |              | RAL          | DE    | REG SEL    |          | NØP         | Y              | F <sub>†</sub> 1 | FL           | 123          |             | Fi. 1        | FLI            | 13 LF XYST RES DATA                                                                                          | 2            |

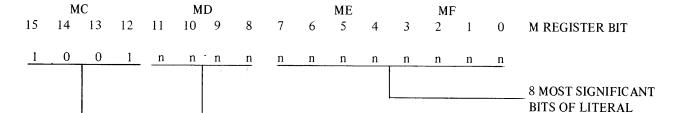

| 8C         | LITERAL<br>MOVE 24 BIT       |     | 0     | 0        |             |              | SEL I | S 2.<br>R GRO | UP,  |               | 8 1          | иоэт        | SIGN       | IFICA    | NT BI        | T5 OF        | -     | TW SIGN:   |          | +           |                |                  |              |              |             |              |                | IS CO CPU WRIT NULL                                                                                          | 8113         |

| 9C         | LITERAL<br>SHIFT/ROTATE      |     |       |          | 0           | R            | EL 5  | EL 15         | 2.   | SNK           | F L          | JLL 2       |            |          |              | -<br>/ROTA   | TE    | 5/R VAR    | . +      | SHFT        | ROT            |                  |              |              |             |              |                | 1                                                                                                            |              |

| 10 C       | T REG                        | '   | . 0   | <u> </u> |             |              | GRO   | UP            |      |               | CT           | VAR         | FX         |          | CTIO         | T<br>N FIEI  | LD    | SINK REG   | <u>-</u> |             | L              |                  |              |              |             |              |                | 1 ,                                                                                                          |              |

| IIC        | EXTRACT FROM<br>T REG        |     |       |          | · · · · · · |              |       | RACTI         | ON F | LD            | COL          | )E          |            |          | VIDT         | н            |       | CODE :     |          | ×<br>+      | _              | Т                | L .          | <del> </del> |             | <del>}</del> | -              | INDIVIDUAL BITS OF SOME 4-BIT                                                                                | #   E        |

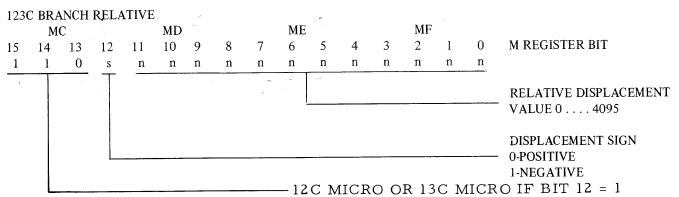

| 123C       | BRANCH<br>RELATIVE           | '   | l<br> | 0        | SGN         | ļ <u>.</u>   |       |               |      | E DIS         |              |             |            |          |              |              |       | DSP SIG    |          |             |                |                  |              | -            |             |              |                | REGISTERS HAVE SPECIAL MEANINGS AS NOTED BELOW:                                                              | <u>a</u>     |

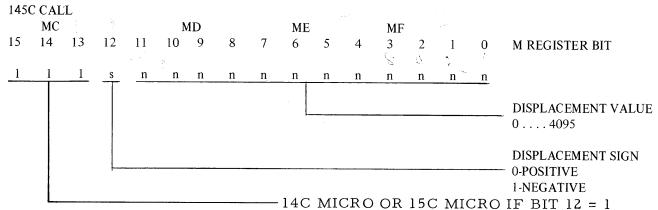

| 145C       | RELATIVE                     | 1   | 1     | 1        | DSP<br>SGN  |              | RE    | LAT           | VE ( | CALL          | ED A         | DDRE        | .55 N      | MAG      | NITI         | UDE          |       | DSP SIG    | 7: -     | +           |                |                  | -            | ├            |             |              |                | NOTE: BITS ARE NUMBERED HERE ACCORDING TO THE HARDWARE                                                       | Introduction |

| }          |                              |     |       |          |             |              |       |               |      |               |              |             |            |          |              | -T           | T     |            | _        |             |                |                  | <del> </del> | ļ            |             | -            | -              | CONVENTION :                                                                                                 |              |

| <u>-</u>   |                              |     |       |          |             |              |       |               |      |               |              |             |            | <u> </u> |              |              |       | W (14 1/A) | <u>.</u> |             |                | -                | ļ            |              |             | <u> </u>     | -              | 3 0,5 0,3 0,3 0,3 0<br>MSB L L5B                                                                             | and          |

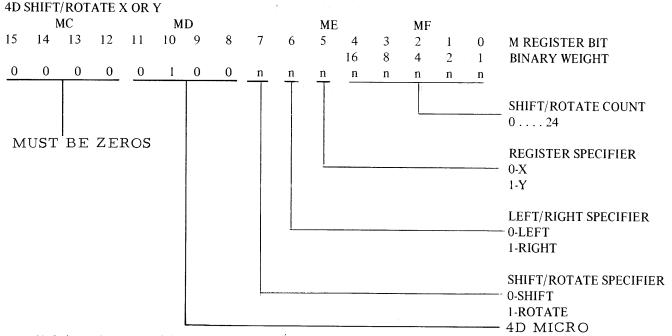

| 40         | SHIFT/ROTATE<br>X OR Y       | ٥   | 0     | 0        | 0           | 0            | ı     | 0             | 0    | VARI          | TNA          | VAR         | SHIF       | T/RO     | TATE         | COU          | NT    | X/Y VAR    | : 1      | SFT+        | SFT-           | ROT-             | ROT →        |              |             | <u> </u>     | -              | M5B L L5B<br>23 00                                                                                           |              |

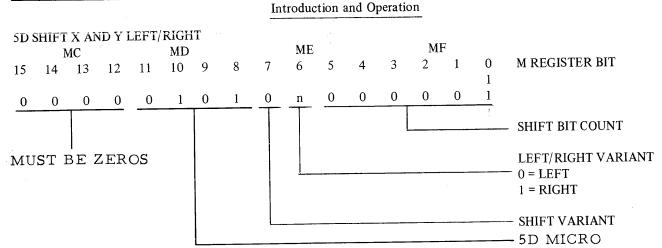

| 50         | SHIFT/ROTATE                 | 0   | 0     | 0        | 0           | 0            | 1     | 0             | ı    | 5/R,I<br>VARI | ANT          |             | FT/        | ROTA     | TE C         | MA X<br>THUO |       | 5/R, DIR   | T5: 1    |             | SFT-           | RES.             | RES.         | ļ            |             | ļ            |                | BIT # BICH XYCH XYST FLCH                                                                                    | 郞 :          |

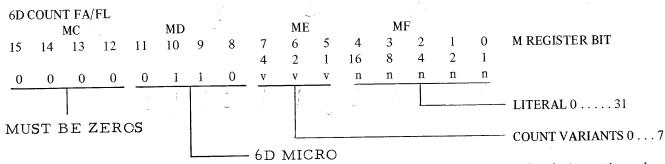

| 6 D        | COUNT FA/FL                  | 0   | 0     | 0        | 0           | 0            | ı     | 1             | 0    |               | AT FA        |             | -          | MA       | AGNIT        | UDE          |       | FL VAR     |          | NØP         | FAI            | FL+              | FA 1         | FA +         | FA +        | FL+          | FA +           | 0 CYL X>Y X \$ 0 FL \$ 0<br>1 CYD X <y \$="" 0="" 5fl<br="" <="" fl="" y="">2 CYF X=Y 1NT OR FL &gt; 5FL</y> | eration      |

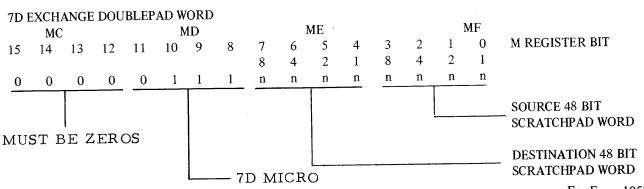

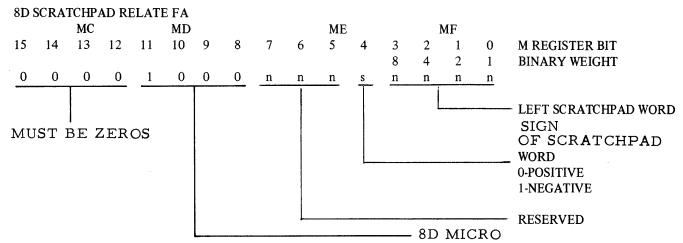

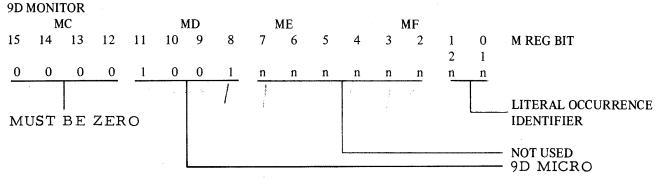

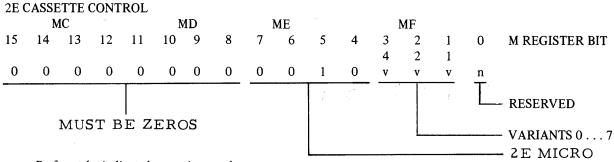

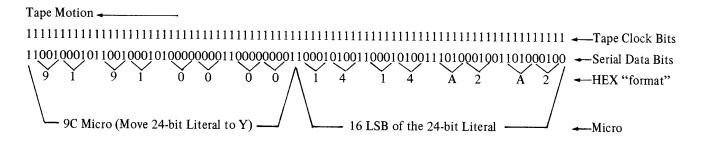

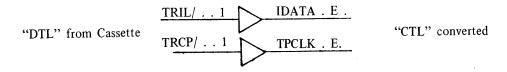

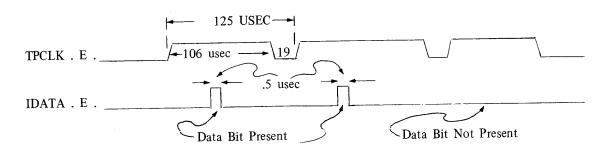

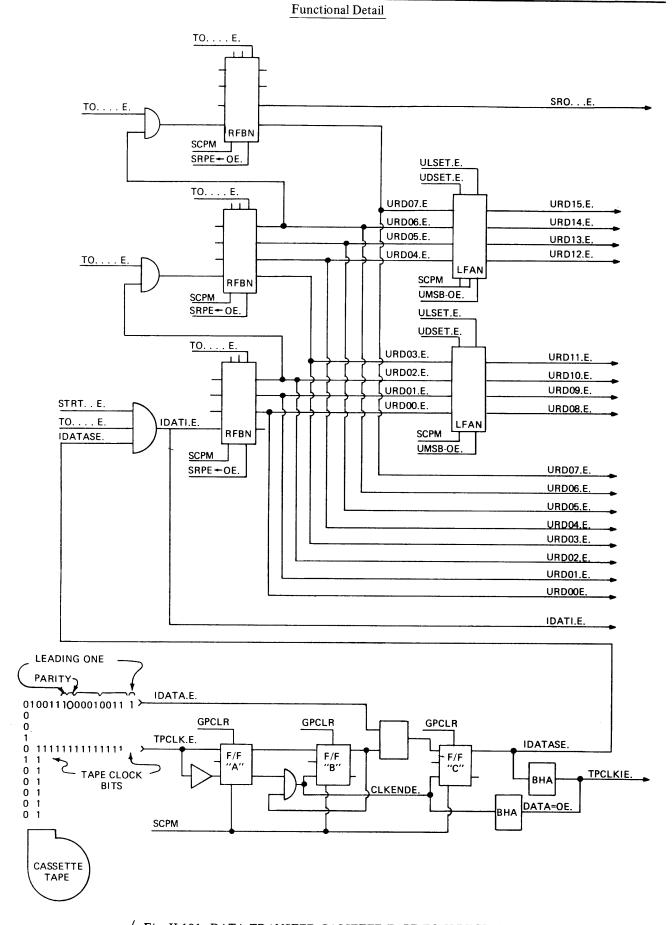

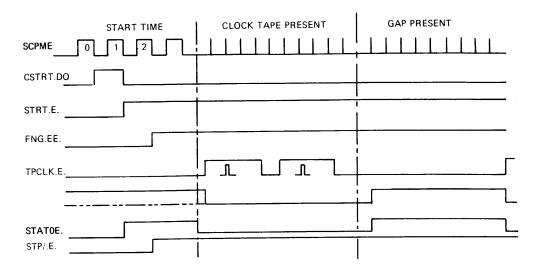

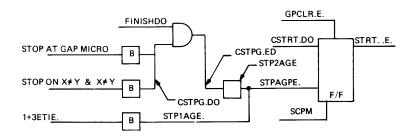

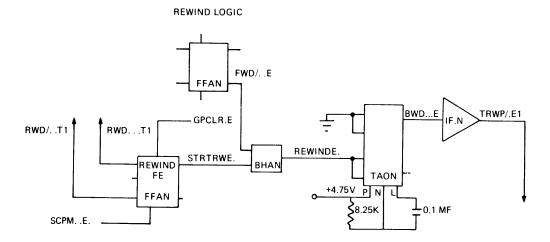

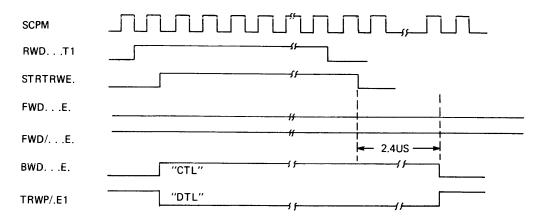

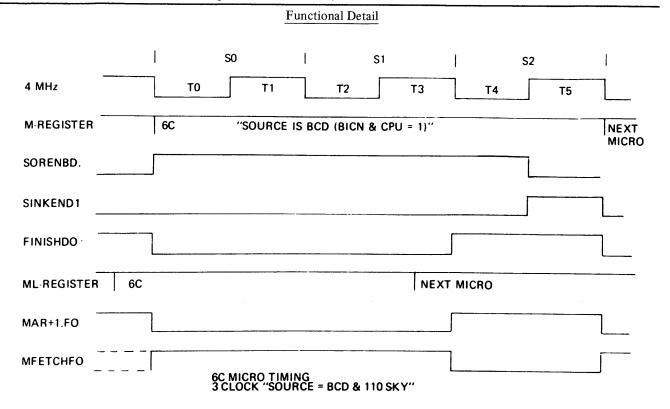

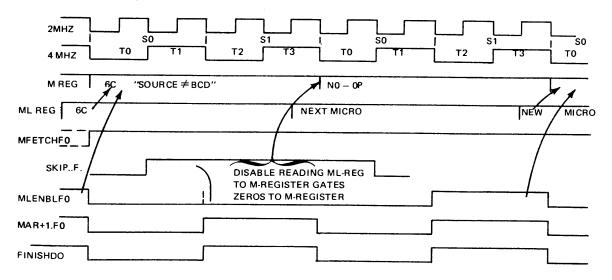

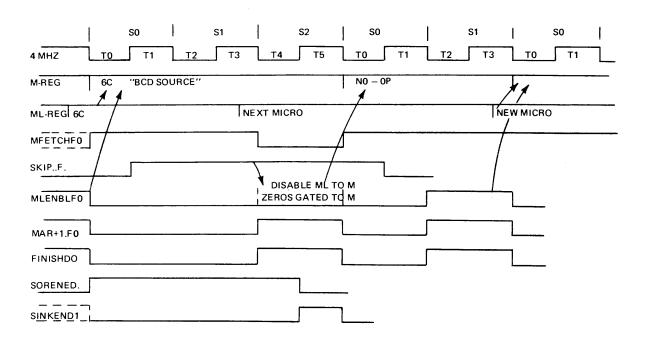

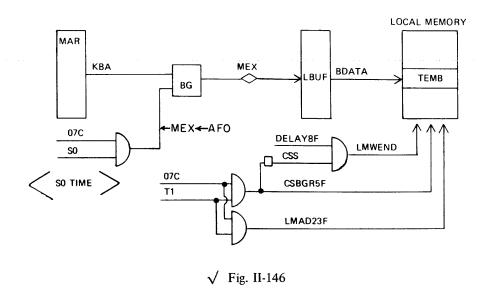

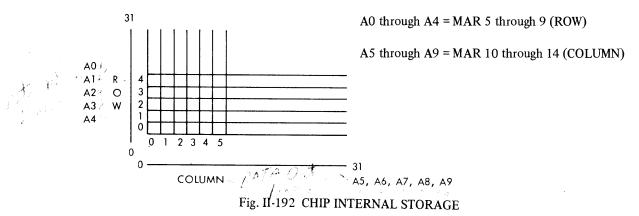

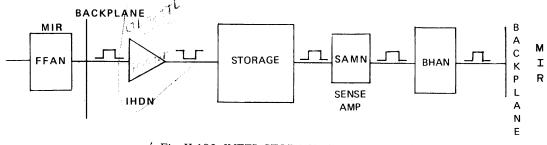

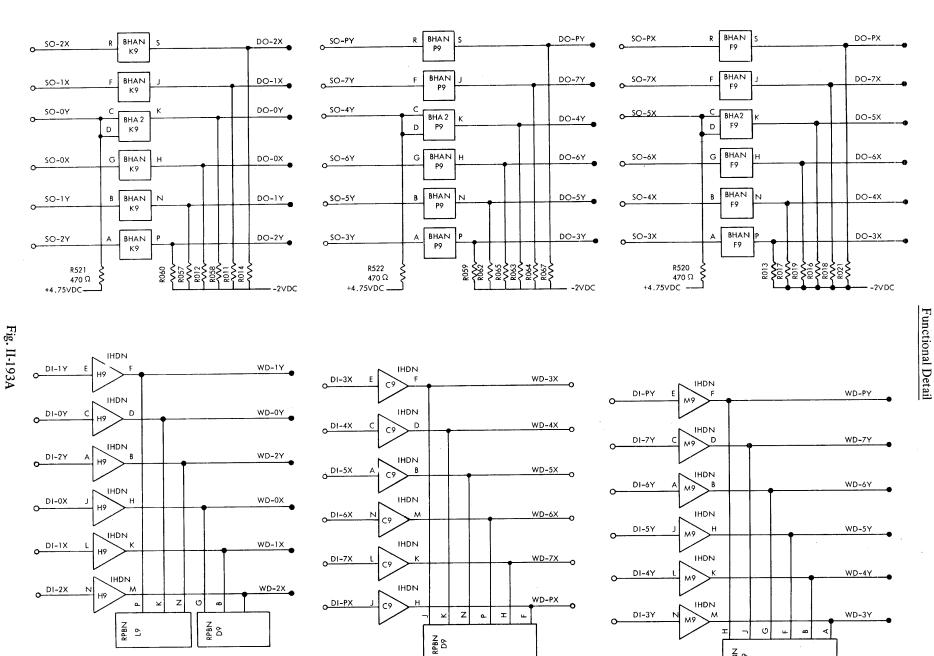

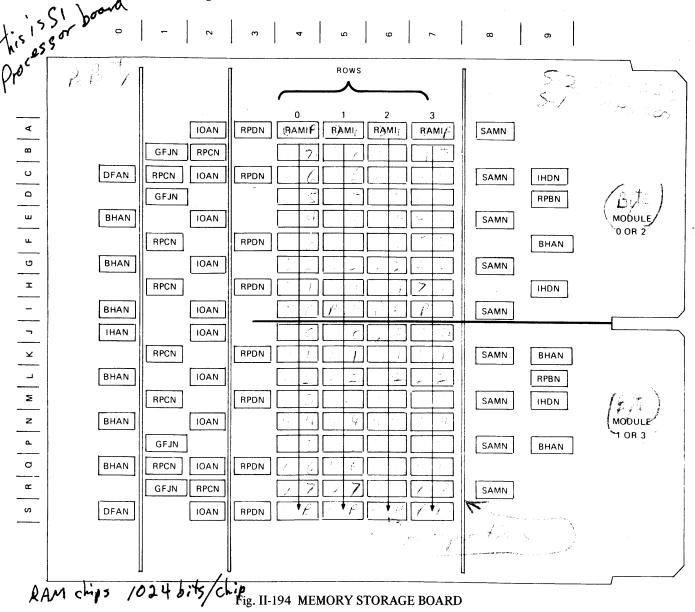

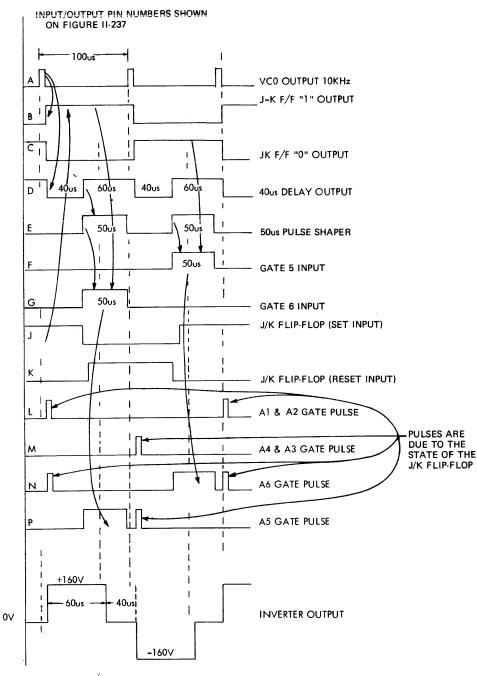

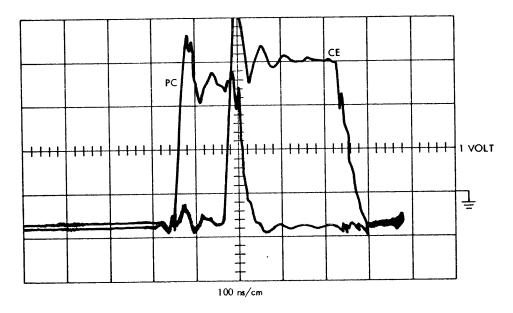

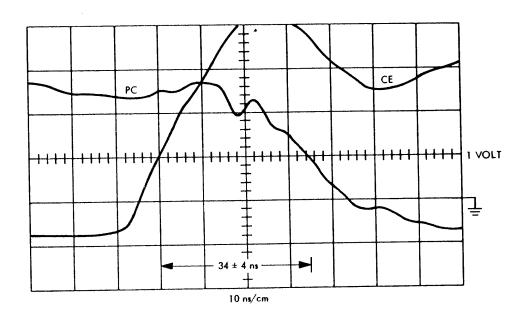

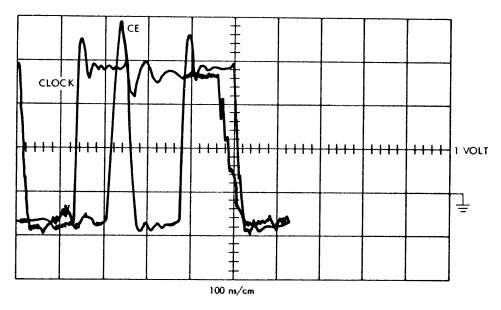

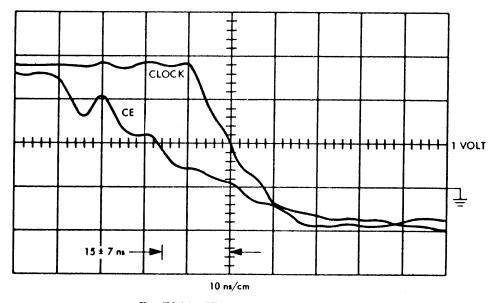

| 7 D        | EXCHANGE DPW                 | 0   | 0     | 0        | 0           | 0            | 1     | ı             | 1    |               | SINK         | DPW<br>ESS  |            |          |              | RESS         |       |            |          |             |                |                  |              | ļ            |             | <u> </u>     |                | 3 LSUY MSBX LSUX FL-SFL<br>INT OR * ANY 1 OR MORE OF :                                                       | 101          |